ARC-V RPX Series Functional Safety Processor IP

The ARC-V™ RPX-110 series functional safety (FS) processors, which include the RPX-110-FS, RPX-115-FS, RPX-110V-FS, and RPX-115V-…

Overview

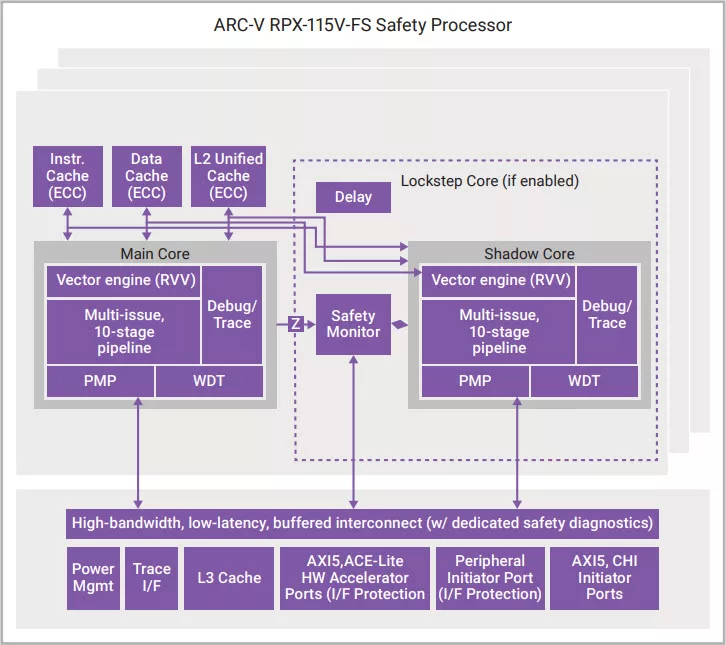

The ARC-V™ RPX-110 series functional safety (FS) processors, which include the RPX-110-FS, RPX-115-FS, RPX-110V-FS, and RPX-115V-FS processors simplify development of high-performance safety-critical applications and accelerate ISO 26262 certification for automotive system-on-chips (SoCs). The Automotive Safety Integrity Level (ASIL) D compliant processors feature a pre-verified dual-core lockstep implementation including an integrated safety monitor. Additionally, they offer the flexibility to operate in an independent “hybrid” mode for ASIL B or non-automotive applications that demand higher performance from the same design.

The ARC-V RPX-110 series FS processors are backed by comprehensive safety documentation, including FMEDA reports, and are supported by the ARC-V® MetaWare Toolkit for Safety. This toolkit includes a certified ASIL D compliant compiler, to generate ISO 26262 compliant code.

Key features

- Dual-issue, 64-bit RISC-V processors for performance efficient host application

- Configurable solution to support both ASIL B (Single core mode) and ASIL D (Dual core lock step), as defined by ISO 26262

- Multicore processor versions: up to 16 CPU cores, 12 HW accelerators

- Per-core configurable in lockstep or hybrid mode: Up to 16x ASIL B or 8x DCLS (ASIL D) cores

- HW safety features: ECC, integrated user-programmable windowed watchdog timer, E2E for buses/data-path, RAS registers, lockstep and integrated safety monitors

- RVA22 and optionally RVA23 RISC-V profile compliant

- Virtualization support through H-extension

- Up to 64 KB L1 instruction and data cache, optional unified private L2 cache of size 1 MB (shared between main core and shadow core if ASIL D selected), up to 64 MB of L3 shared cluster cache

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is ARC-V RPX Series Functional Safety Processor IP?

ARC-V RPX Series Functional Safety Processor IP is a CPU IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.