Configurable CPU tailored precisely to your needs

The TES µEngine concept enables complex digital circuit tasks to be created as software-defined functions executed by mini-comput…

Overview

The TES µEngine concept enables complex digital circuit tasks to be created as software-defined functions executed by mini-computers. Each task is assigned to a dedicated µEngine optimized for efficiency, deterministic behavior, and real-time performance.

CONCEPT

A µEngine is based on a configurable CPU called µCore. The µCore remains in source code until a generator creates its synthesizable HDL code according to a specific configuration. Only the required hardware components for the instruction set are generated, keeping the size minimal. Combined with memory and peripherals, the µCore forms the µEngine. Tasks can be defined in C language and are stored in ROM, making the µEngine a true “Software Defined Device”.

Advantages of this approach include decoupling hardware and software development, reducing time-to-market, and enabling late-stage software changes. Programmable ROM options (OTP, EEPROM, Flash) allow updates even after tape-out or in-field use.

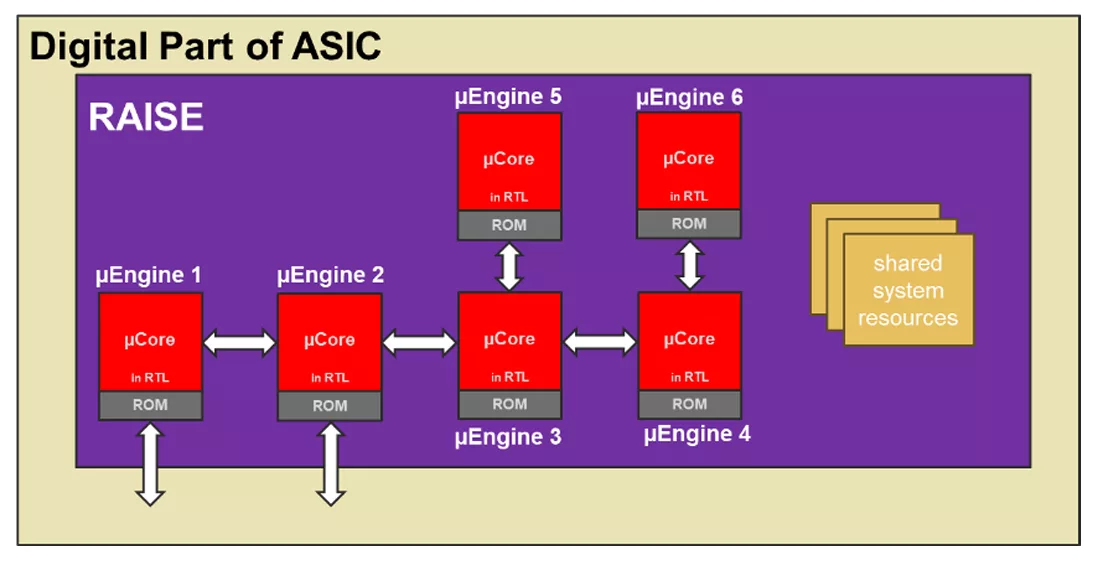

RAISE SYSTEM

The RAISE system (Related Array of Independent Single-tasking µEngines) supports the parallel execution of different tasks, enabling the efficient implementation of complex operations. Each µEngine can be optimized for its specific function and disabled when not needed to save power.

An entire RAISE system with multiple µEngines operating in parallel, can be cycle-accurately simulated on a PC, ensuring predictable runtime and avoiding hardware dependency during early development.

Block Diagram

Benefits

- Increased efficiency by converting digital design into software development

- Hardware independent and parallel Software development

- Rapid system development and evaluation:

- Software debug and tests with RAISE Simulator

- Peripherals modeled as executable Python scripts

- Evaluation of system functionality during design and conception

- Cycle-accurate instruction simulation

- Ready-to-use: Verified IP block reuse reduces verification effort

- Reduced simulation effort – software changes do not require gate-level simulation

- Flexibility and maintainability through software updates without RTL changes

- Faster time-to-market via accelerated development

Applications

- Complex state-machines

- Digital filters

- Interface controllers

- Protocol converters

- Hardware accelerators

- Specialized embedded microcontrollers

- Specialized parallel processor structures

- Feedback loop controllers (PD, PI, PID)

- Brushless DC motor controllers

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Configurable CPU tailored precisely to your needs?

Configurable CPU tailored precisely to your needs is a CPU IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.