Compact Embedded RISC-V Processor

The BA5x-CM is a feature-rich 32-bit deeply embedded processor.

Overview

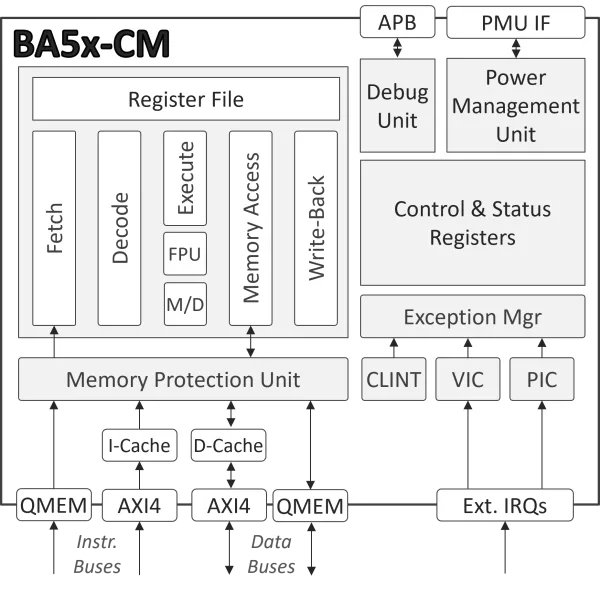

The BA5x-CM is a feature-rich 32-bit deeply embedded processor. Equipped with a floating-point unit and an instruction cache memory and supporting concurrent execution in a multiprocessor environment, it is well-suited to a wide range of edge IoT and similar applications.

The two- or five-stage pipeline processor implements either the RV32I or RV32E instruction set and comes pre-configured with the RISC-V extensions necessary for a multi-threaded RTOS with hardware-supported floating-point calculations: Multiply/Divide (M), Compressed Instruction (C), Single-Precision Floating-Point (F), Zifencei, and Atomic Instructions (A). The Code Size Reduction (Zc) extension is also enabled to further support low-power IoT designs.

The core’s small silicon footprint, starting at 90k gates, minimizes leakage currents while idle and reduces dynamic power consumption. The BA5x-CM also features low-latency and predictable-time interrupt response thanks to its VIC (Vectored Interrupt Controller), which supports up to 64 interrupt sources. Additionally, the BA5x-CM is also equipped with a configurable size (up to 64 kB) and associativity (up to 4-way) instruction and data caches, to reduce instruction and data fetch latency and power consumption, and improve performance when executing from a slow or high-latency memory (e.g., off-chip flash memory, or DRAM).

The compact BA5x-CM is exceptionally efficient and scores 2.53 to 3.0 Coremarks/MHz (more processing power per MHz than most processors in its class). This allows operating the core at low frequencies to further save power, or meeting more demanding embedded processing requirements, or any optimum combination of both.

Easy Integration and Low Risk

The processor core uses AMBA® AXI4 or AHB-Lite, and low-latency Quick-access Memory (QMEM) interfaces for fetching instructions and accessing data and peripherals. The debug unit connects to an external JTAG/TAP controller via an APB port.

Part of the family of processor cores available from CAST for more than a decade and used by hundreds of customers, the BA5x-CM IP core has been designed for easy reuse and integration, has been rigorously verified, and is LINT-clean, scan-ready, and silicon-proven. It is available in Verilog source code.

Software Development

The BA5x-CM can be used with RISC-V compatible toolchains, libraries, and IDEs, or the included BeyondStudio™ IDE. This Eclipse-based Integrated Development Environment combines an instruction-level simulator and the latest version of the RISC-V GNU toolchain. Employed by numerous BAx processor users for over a decade, BeyondStudio is a complete and fully featured IDE.

Reference designs on FPGA development boards are available to ease evaluations and accelerate code development. Contact CAST Sales for more information.

Key features

Compact & Efficient Architecture

- Small silicon footprint for lower leakage and dynamic CPU power

- From 90k gates

- Advanced power management

- Dynamic clock gating and unused units power shut off

- Software- and hardware-controlled clock frequency scaling

- Single-issue, in-order, 2 or 5-stage pipeline

- Harvard architecture with separate instruction and data AXI-Lite and Quick-access Memory (QMEM) buses

- Optional instruction and data caches with synthesis-time configurable associativity and size

Performance

- 3.0 or 2.53 (5-stage) Coremarks/MHz

- Over 500 MHz in 16 nm

RISC-V Features

- 32-bit Base RISC-V ISA (RV32I/E) with Compressed Instructions (C), Multiply/Divide (M), Single-Precision Floating Point (F), Atomic Instructions (A), Code Size Reduction (Zc), and Fence.i (Zifencei)

- Supervisor, User, and Machine Modes

- Core Local Interrupt Controller (CLINT) for timer and software interrupts

- Programmable Interrupt Controller (PIC) for up to 64 direct external interrupts

- Physical Memory Protection (PMP) with up to 16 regions

- Wait-for-Interrupt (WFI)

Available Pre-Integrated Platforms

- Bus fabric with peripherals such as GPIO, UART, Real-Time Clock, Timers, I2C, and SPI

- Optionally customized to include memory controllers, interconnects, and more from the CAST IP line

Low Risk & Flexible Licensing

- Industry-standard licensing terms with royalty-free options

- Reliable vendor with an extensive track record and excellent support

- Thousands of IP core licenses, and billions of units shipped with IP from CAST since 1997

- Experienced and responsive support team with a 24/7 culture

Debug and IDE Support

- JTAG Debug with hardware triggers

- Use standard RISC-V IDEs or the included Eclipse-based BeyondStudio™

Block Diagram

What’s Included?

- The core is available for ASICs in synthesizable Verilog.

- It includes everything required for successful implementation: extensive documentation, a testbench, a sample SoC design, and sample synthesis and simulation scripts.

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Compact Embedded RISC-V Processor?

Compact Embedded RISC-V Processor is a CPU IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.