8-stage dual issue, in-order, superscalar processor with dual vector processing units (1024-bit VLEN/512-bit DLEN)

The second generation SiFive® Intelligence™ X390 is an 8-stage dual issue, in-order, superscalar processor with dual vector proce…

Overview

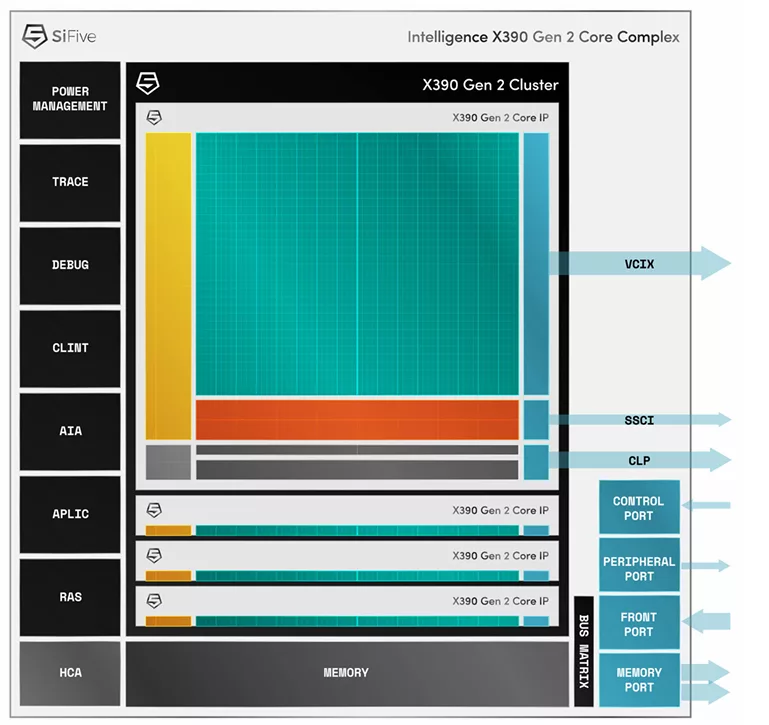

The second generation SiFive® Intelligence™ X390 is an 8-stage dual issue, in-order, superscalar processor with dual vector processing units. It scales to a 4-core cache-coherent complex with optional SiFive Scalar Coprocessor Interface (SSCI) and Vector Coprocessor Interface eXtensions (VCIX) for close coupling with customer-designed external AI accelerators or other coprocessors.

The X390 Gen 2 introduces an efficient memory subsystem, configurable load queues to hide memory latency and targeted instructions for speeding up AI/ML workloads. The X390 Gen 2 delivers 4x compute and 32x data throughput compared to the popular X280 Gen 1, while enabling up to 1TB/s data bandwidth in a four-core configuration.

Use X390 as a standalone edge AI processor or as an Accelerator Control Unit, with your custom accelerator, to perform control and assist functions and simplify the software stack.

Key features

- New in Second Generation

- New RVA23 support

- New RVV1.0 512-bit vector engine

- New SSCI interface added alongside VCIX

- New instructions and extensions

- New improved memory subsystem

- New memory latency tolerance

- New HW support of BF16 datatype

- New vector crypto support

- Plus many other new features, enhancements and upgrades

- RISC-V Vector extension supported

- Up to 1024-bit VLEN Dual Vector ALU

- 512-bit DLEN

- SiFive Intelligence Extensions for ML workloads

- New hardware accelerated Exponential Instructions

- Custom instructions to greatly accelerate Neural Network computation

- Optimized neural network libraries and Open XLA support

- 1024-bit vector register length processor

- Variable length operations, up to 512-bits of data per cycle

- Ideal balance of control logic and data parallel compute

- Decoupled Vector pipeline

- INT8 to INT64 integer data type

- BF16/FP16/FP32/FP64 floating point data type

- Built on silicon-proven U7-Series core

- 64-bit RISC-V ISA

- 8-stage dual-issue in-order pipeline

- Coherent multi-core, Linux capable

- High performance vector memory subsystem

- Shared L2 Cache architecture optimized for vector compute

- Dedicated uncached data movement port

- Multi-core processor configuration, up to 4 cores

- SSCI and VCIX specialized interfaces for close coupling with customer-designed external AI accelerators or other coprocessors

- SiFive Scalar Coprocessor Interface (SSCI) to issue custom instructions to accelerators for optimum scheduling at lower latency

- Vector Coprocessor Interface eXtensions (VCIX) allowing custom vector instructions to be executed on the accelerator at high bandwidth from the vector pipeline

Block Diagram

What’s Included?

- RTL Evaluation

- Test Bench RTL

- Software Development Kit

- FPGA Bitstream

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 8-stage dual issue, in-order, superscalar processor with dual vector processing units (1024-bit VLEN/512-bit DLEN)?

8-stage dual issue, in-order, superscalar processor with dual vector processing units (1024-bit VLEN/512-bit DLEN) is a CPU IP core from Sifive, Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.