32 Bit - Embedded RISC-V Processor Core

The L31(F) is a small, efficient 32-bit embedded RISC-V processor aimed at embedded systems with more modest processing requireme…

Overview

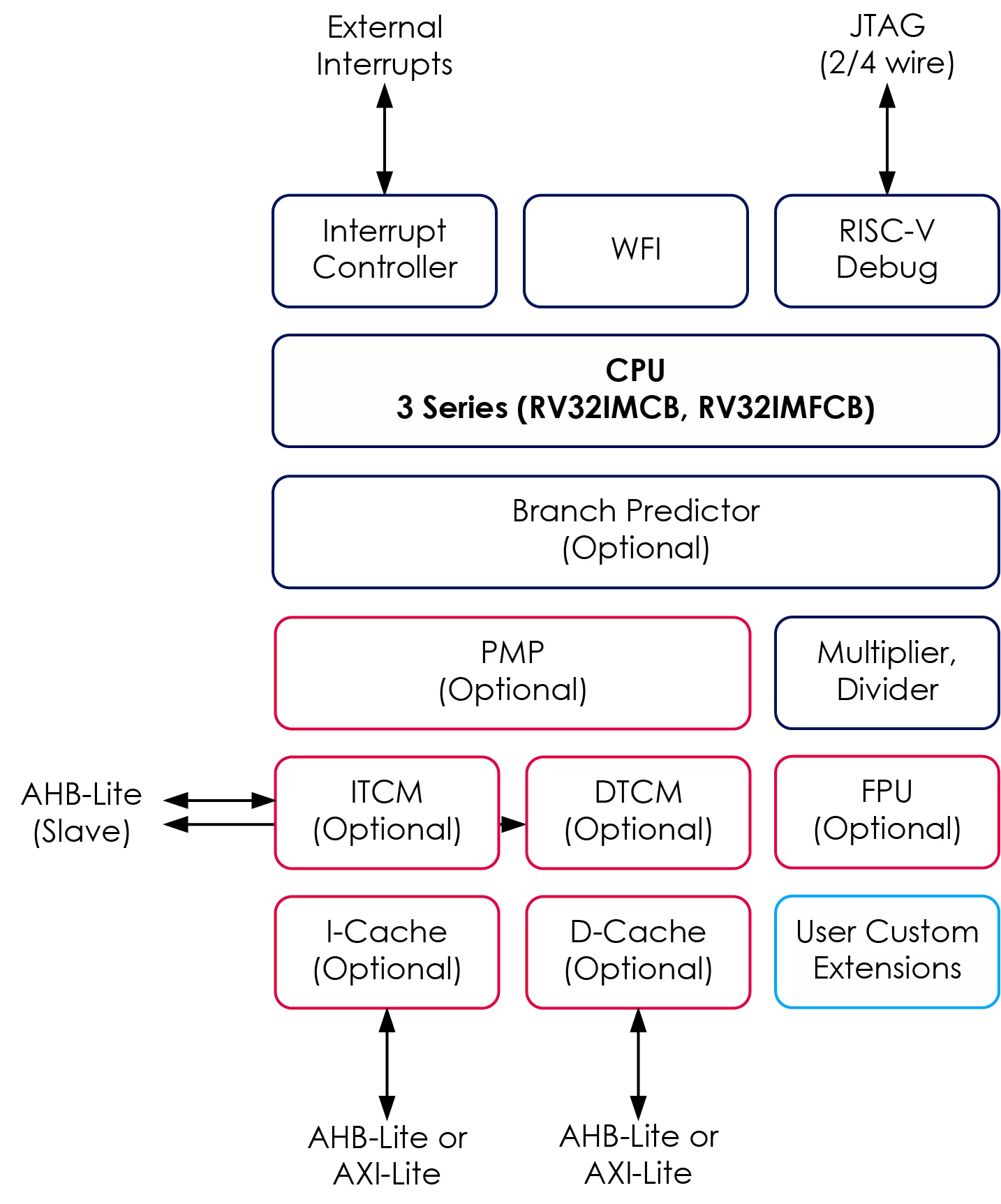

The L31(F) is a small, efficient 32-bit embedded RISC-V processor aimed at embedded systems with more modest processing requirements. The core has a 3-stage pipeline and has 32 general-purpose registers.

The core includes optional L1 data and instruction caches, optional instruction and data TCM, optional 8 or 16 PMP regions, an interrupt controller and RISC-V Debug module optionally with PC trace.

Like with all Codasip RISC-V cores, it is possible to create custom instructions using Codasip Studio to extend the L31 and to generate corresponding hardware and software development kits.

Key features

- 32-bit RISC-V core

- Available in two versions:

- RV32IMC

- RV32IMCF

- 32 general purpose registers

- Either parallel multiplier

- 3-stage pipeline

- Dynamic branch predictor

- RISC-V privilege mode support:

- Machine, User

- Internal interrupt controller

- Up to 256 sources

- Optional FPU (L30F)

- Optional instruction and data tightly coupled memories (TCM)

- Optional 8 or 16 PMP regions

- Optional L1 data and instruction caches

- Standard RISC-V CLINT

- Up to 256 sources

- Wakeup interrupt controller

- NMI

- On-chip debugger

- RISC-V Debug module

- 2/4 pin JTAG

- 2-8 breakpoints/watchpoints

Block Diagram

Benefits

- Flexibility

- Wide choice of configuration options.

- Customization

- Ability to create custom RISC-V extensions to optimise performance

- Efficient architectural exploration of custom extensions with Studio

- Automatic HDK and SDK generation from Studio

- Rigorous verification of modified L31 core using UVM

- Tensor Flow Lite Micro is supported

Applications

- The L31 is aimed at low- to mid-range embedded applications such as IoT, always on sensors, wireless connectivity, audio, motor control and display control.

What’s Included?

- Human-readable and structured RTL in either:

- Verilog

- VHDL

- System Verilog

- Hardware development kit (HDK)

- Synthesis scripts

- Simulation testbenches

- Debug support

- Software development kit (SDK)

- LLVM C-compiler

- Assembler

- Disassembler

- Linker

- Instruction-accurate simulator

- Cycle-accurate simulator

- Profiler

- Option for extending L31

- CodAL model for Codasip Studio

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 32 Bit - Embedded RISC-V Processor Core?

32 Bit - Embedded RISC-V Processor Core is a CPU IP core from Codasip listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.