32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

The L31AS is a 32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification.

Overview

The L31AS is a 32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification. Part of our safety and security offering, this embedded processor is ideal either as a Main Controller or a Safety Island in a Functional Safety System.

It includes 2 instances of the L31 in a dual-core lockstep configuration along with Physical Memory Protection as a security feature.

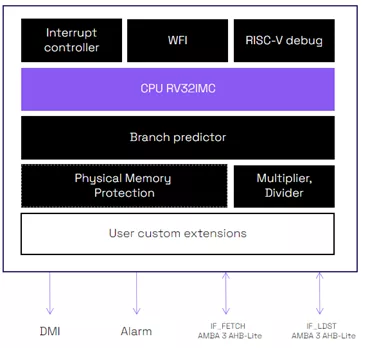

L31AS is an in-order, 3-stage, single-issue RISC-V core targeted for automotive and other functional safety applications. It is based on the RV32IMC ISA. It includes physical memory protection.

L31AS features separate Data and Instruction AHB-Lite interfaces, block-level gating in single-core configuration and performance counters. It uses the standard RISC-V debug specification with 4 debug triggers and Debug Memory Interface (DMI) as an APB interface that can be used to interface with external debuggers.

Certified for Functional Safety

The L31AS core is certified by TÜV SÜD according to the requirements set forth in ISO26262 up to ASIL B. It is delivered with a safety pack including a safety manual and a safety case report.

Software development

Using standard AMBA AHB Interface, L31AS can easily be connected to existing systems and interconnects. What is more, L31AS is designed to simplify software development, with essential features to support developers:

- Debug interface – using standard RISC-V Debug specification

- Instruction-accurate model – for fast execution of software, before hardware is available

- Cycle-accurate model – for software algorithm optimization, when time constraints require precise execution

- Full trace capability – in the cycle-accurate model, to hunt hard-to-find bugs

Key features

- Flexible use cases

- Safety Island as a protected enclave of the device providing freedom of interface for the independent execution of safety-related application code.

- Controller, running the safety-related application code.

- Proven technology

- Based on the L31 silicon-proven embedded processor

- State-of-the-art verification scheme brings quality and reliability

- State-of-the-art safety and security

- Dual-core lockstep provides a robust and well trusted approach to building high-reliability systems and meeting the stringent safety requirements of critical applications

- L31AS increases security against certain threat scenarios and can help meet requirements for security certification

Block Diagram

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification?

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification is a CPU IP core from Codasip listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.