MIPI I3C Master RISC-V based subsystem

RISC-V based MIPI I3C master interface has been developed to ease sensor system design architectures in mobile wireless products …

Overview

RISC-V based MIPI I3C master interface has been developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors. All the basic functionalities of MIPI I3C master has been proved with Microsemi smart fusion 2 creative development board .In addition the MIPI I3C master supports for both AHB lite and APB Interface.

Key features

- Dynamic address assignment.

- Host controller compliance

- SDA arbitration.

- Data transfer with and without broadcast.

- All basic CCC command features.

- Both push-pull and open drain mode transaction.

- Private write and read operations.

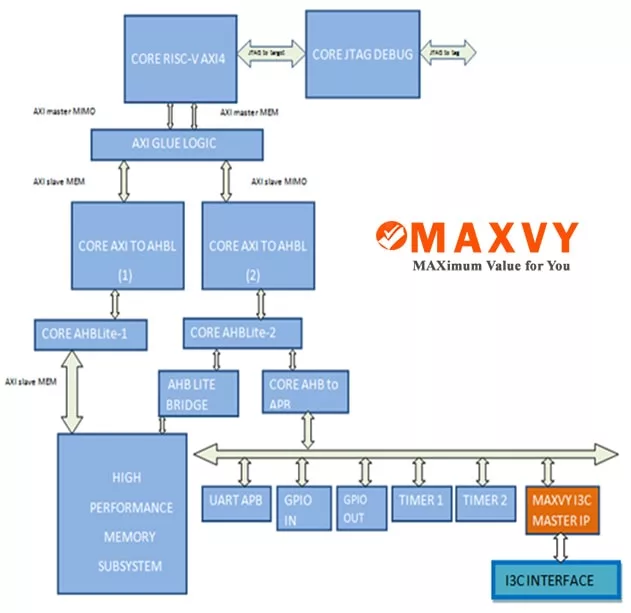

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is MIPI I3C Master RISC-V based subsystem?

MIPI I3C Master RISC-V based subsystem is a CPU IP core from MAXVY Technologies Pvt Ltd listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.