JESD204 FPGA IP

The JEDEC committee created the JESD204 data converter serial interface standard to standardize and reduce the number of data inp…

Overview

The JEDEC committee created the JESD204 data converter serial interface standard to standardize and reduce the number of data inputs/outputs between high-speed data converters and other devices, such as FPGAs. The protocol has many advantages, such as simplified layouts, skew management, and deterministic latency.

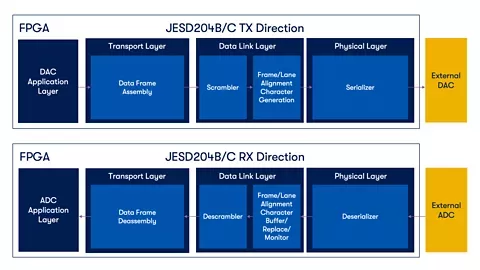

Altera JESD204 IP simplifies the integration of high-speed data converters with digital processing systems. The IP supports data rates as high as 32.44 Gbps and manages the physical, data link, and transport layers while simplifying configuration, clock synchronization, and data transmission.

IP is pre-verified and JEDEC Compliant which is crucial for ensuring interoperability and reliability in high-speed data applications. The IP includes design examples simplifying integration and enabling ease-of-use reducing development time for designers.

Block Diagram

Applications

- Wireless Communications

- Radar and Defense Systems

- Medical Imaging

- Broadcast

- Test and Measurement Equipment

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

What is JESD204C? A quick glance at the standard

Frequently asked questions about JESD204 IP cores

What is JESD204 FPGA IP?

JESD204 FPGA IP is a JESD204 IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.