JESD403 VIP

The SmartDV Verification IP (VIP) for JESD403 provides an efficient and simple way to verify the JESD403 bidirectional two-wire s…

Overview

The SmartDV Verification IP (VIP) for JESD403 provides an efficient and simple way to verify the JESD403 bidirectional two-wire serial interface. The SmartDV VIP is fully compliant with version 1.0 specifications.

JESD403 VIP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

JESD403 VIP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compliant with JESD403 version 1.0 specification.

- Full JESD403 Host Controller and Device functionality.

- Two wire serial interface up to 12.5 MHz.

- Supports Dynamic Address Assignment including Static Addressing for legacy I2C Devices.

- In-Band Interrupt support.

- Support for all JESD403 Common Command Codes (CCC's).

- 7-bit configurable Slave Address.

- Supports HOST DEVICE ADDRESS.

- Supports Timed reset.

- Supports Write/Read formats.

- Supports PEC enable/disable.

- Master SCL clock stalling is supported.

- Slave supports control of response fields including NACK, Data and Slave busy.

- Supports slave error types S1 and S2.

- Supports injection of various errors.

- Master aborting in middle of access

- Master doing ACK on last read access

- Callbacks in Master, Slave and Monitor for user processing of data

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Functional coverage of complete JESD403 specs.

- JESD403 Verification IP comes with complete testsuite to test every feature of JESD403 specification.

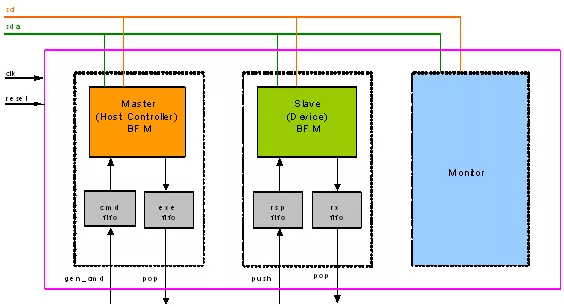

Block Diagram

Benefits

- Faster testbench development and more complete verification of JESD403 designs.

- Easy to use command interface simplifies testbench control and configuration of TX and RX.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the JESD403 testcases to certify JESD403 Slave/Master device

- Examples showing how to connect various components and usage of Master, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

What is JESD204C? A quick glance at the standard

Frequently asked questions about JESD204 IP cores

What is JESD403 VIP?

JESD403 VIP is a JESD204 IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.