Simulation VIP for JESD204

Cadence provides a mature and comprehensive Verification IP (VIP) for the JESD204 protocol.

Overview

Cadence provides a mature and comprehensive Verification IP (VIP) for the JESD204 protocol. Incorporating the latest protocol updates, the Cadence® Verification IP for JESD204 provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for JESD204 helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog verification language along with associated methodologies, including the Universal Verification Methodology (UVM).

Supported Specification: JESD204B and JESD204C

Key features

- Topology

- Transmitter or receiver configuration

- Clock Frequency

- Any frequency is supported, as the VIP works on the source clock

- Initial Lane Alignment

- Enabling or disabling initial lane alignment

- Encoding Type

- 8b10, 64b66b, and 64b80b encoding modes

- 64-bit Sync Header

- Transmission of all types of sync header information, such as, FEC, CRC-3, CRC-12 and command channel

- Subclass

- Subclass0, subclass1, and subclass2

- Scrambling

- Supports scrambling with user-specific initial seed value

- Character Replacement

- Character replacement feature with and without scrambling

- Deterministic Delay

- Deterministic delay for subclass 1 and 2

- Transport Layer Parameter

- Config/register to control transport layer features, such as CS, HD, and F

- Lane Control

- Lane ranging from 1 to 32

- Lane to Lane Delay

- Transmission and reception for cases where lanes are not aligned

- Test Mode

- Layer-wise test mode

- Transport Layer Bypass

- Skip transport layer operation like padding tail bits

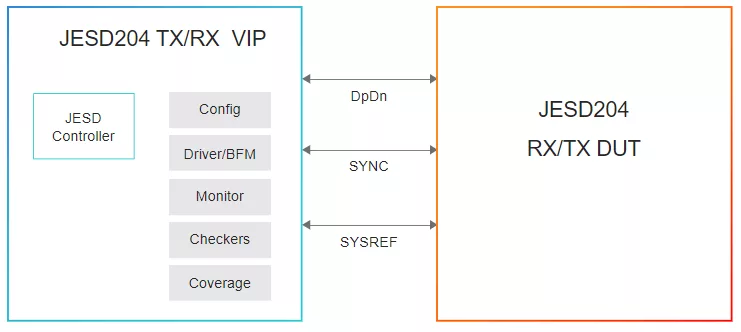

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

What is JESD204C? A quick glance at the standard

Frequently asked questions about JESD204 IP cores

What is Simulation VIP for JESD204?

Simulation VIP for JESD204 is a JESD204 IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.