JESD204 Verification IP

This JESD204 Verification IP provides an and efficient solution for verifying and debugging these standards in a UVM simulation e…

Overview

This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product. The JESD204 VIP is prepared for seamless functionality on all major simulators with UVM support and can be used only for JESD204 IPs from Chip Interfaces.

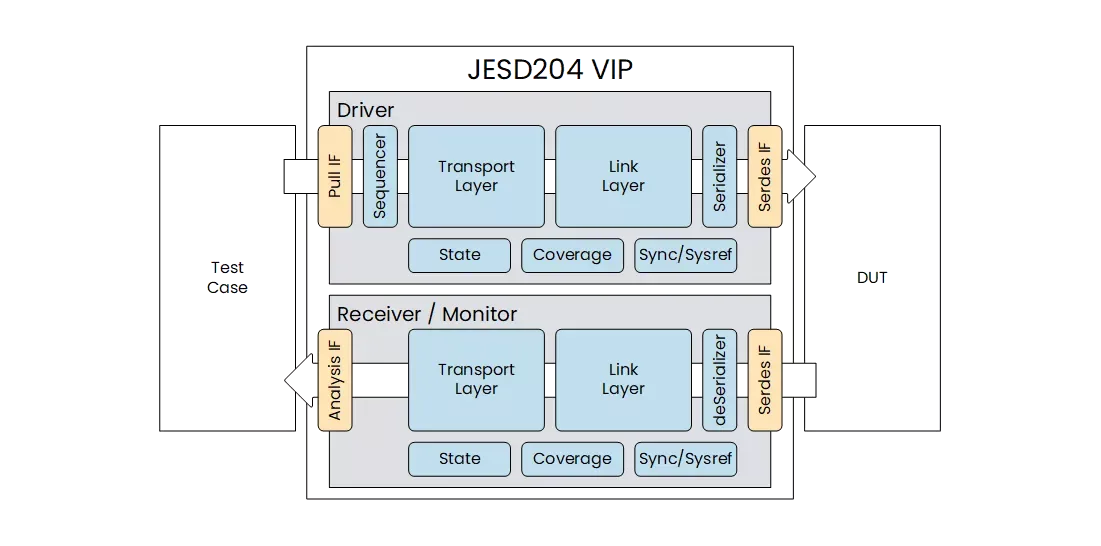

JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging JESD204B, JESD204C, and JESD204D standards in a UVM simulation environment, based on a verification IP. The driver will send test case controlled JESD traffic on the Serdes interface to the DUT RX. DUT TX traffic will be received and monitored.

Running regression for coverage is supported and the solution is delivered with Integration Test environment to the Chip Interfaces JESD204 IP, such that is ready to test for a seamless out of the box experience.

Key features

- Supports 32bit data width per converter

- Supports multiple samples per converter per frame cycle

- Supports up to 24 lanes

- Supports 8b 10b link layer functions.

- Supports 64b 66b link layer functions

- Scrambling

- Forward Error Correction (FEC) – For JESD204C

- Reed-Solomon FEC (RS-FEC) – For JESD204D

- RS-FEC encoding, 64b 66b, 64b 80b and 8b 10b

- Extensive error injection and detection

- Built-in protocol checks

- Supports Lane alignment monitoring, correction and character replacement

Block Diagram

Benefits

- Test Environment: JESD204 IP is Tested against a VIP model in UVM regression for full functional coverage

- Silicon Agnostic: Designed in Verilog and targeting both ASICs and FPGAs

- Interoperability Tested: JESD204 IP is interoperability tested with

- All leading PHY providers

- Key data converter ADC & DAC providers

- PHY Integration: PHY Integration support with additional hours or off the shelf PHY integration package for quick and efficient deployment

- Active Support: All support is actively provided by engineers directly

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note.

- Simulation Environment, including Simple

- Testbed, Test case, Test Script and Random Tests.

- Error Scenario Tests and Basic and Directed Protocol tests (optional).

- Access to support system and direct support from Comcores Engineers.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

What is JESD204C? A quick glance at the standard

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

Frequently asked questions about JESD204 IP cores

What is JESD204 Verification IP?

JESD204 Verification IP is a JESD204 IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.