Highly-optimized PQC implementations, capable of running PQC in under 15kb RAM

PQCryptoLib-Embedded is a versatile, CAVP-ready cryptography library designed and optimized for embedded devices.

Overview

PQCryptoLib-Embedded is a versatile, CAVP-ready cryptography library designed and optimized for embedded devices. With its design focused on ultra-small memory footprint, PQCryptoLib-Embedded solutions have been specically designed for embedded systems, microcontrollers and memory-constrained devices. It provides a PQC integration to devices already in the field.

The software library is highly congurable at build time, which makes it possible to optimize PQCryptoLib-Embedded for binary size, memory-footprint or performance, and means you can deploy the software without changing the underlying hardware (also on legacy devices).

This makes PQCryptoLib-Embedded an ideal solution for PQC-enablement of browneld devices that are already deployed in the eld, especially when it comes to the provision of quantum-safe TLS.

It’s also a consideration for the next generation of devices, as PQCryptoLib-Embedded can be a step towards hardware integration, for example with our PQPlatform products.

PQCryptoLib-Embedded enables secure quantum-resistance on embedded platforms. It’s designed to be compatible with existing architectures and platforms and provides a minimal footprint.

Supported CPU architectures

- X86, x86_64

- ARM64

- ARM Cortex-M3/M4

- RISC-V

Multiple solutions configured to suit your use case

PQCryptoLib-Embedded builds are already available for many use cases and platforms meeting different optimization goals. Other builds can be delivered to meet your specific requirements.

| Solution | Description | FIPS 140-3 CMVP | FIPS 140-3 CAVP | Security Level | PQC Support | Classical support | Platform | Size | Speed |

|---|---|---|---|---|---|---|---|---|---|

| PQS-SW-CLE-1 | ML-DSA/ML-KEM for ARM Cortex-M3 in <15kB RAM | Ready | Ready | Cloud | Narrow | N/A | Arm* | Ultra Small | Low |

| PQS-SW-CLE-2 | LMS/XMSS for RISC-V | Ready | Ready | Cloud | Narrow | N/A | RISC-V* | Small | Low |

| PQS-SW-CLE-3 | ML-DSA/ML-KEM for ARM Cortex-M4 | Ready | Ready | Cloud | Narrow | N/A | Arm* | Small | Med |

| PQS-SW-CLE-4 | DPA Protected ML-DSA Sign Gen for ARM Cortex-M3 | Ready | Ready | Edge | Narrow | N/A | Arm* | Ultra Small | Low |

*ports to target platforms, usually available in ~4 weeks

Key features

- Optimized memory and binary size

- Bare metal implementation

- NIST FIPS 202, 203, 204 compliant (ML-KEM, ML-DSA, SLH-DSA)

- Resistant to time-based SCA

- C interface - integration layer

- External hash engine support

- Product grade solution with full PQShield support

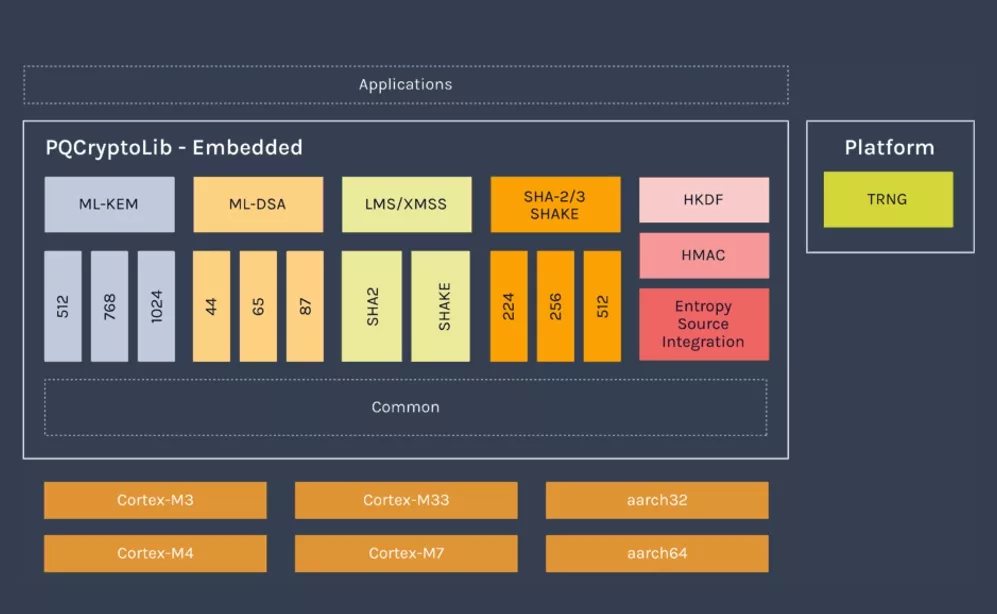

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Post Quantum IP core

How to design secure SoCs Part IV: Runtime Integrity Protection

Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

Deploying StrongSwan on an Embedded FPGA Platform, IPsec/IKEv2 on Arty Z7 with PetaLinux and PQC

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

Why Anti-tamper Sensors Matter: Agile Analog and Rambus Deliver Comprehensive Security Solution

Frequently asked questions about Post-Quantum Cryptography IP cores

What is Highly-optimized PQC implementations, capable of running PQC in under 15kb RAM?

Highly-optimized PQC implementations, capable of running PQC in under 15kb RAM is a Post Quantum IP core from PQShield listed on Semi IP Hub.

How should engineers evaluate this Post Quantum?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Post Quantum IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.