High-performance RISC-V CPU

The second-generation high-performance RISC-V CPU delivers a major leap in compute capability, designed for deployment across dat…

Overview

The second-generation high-performance RISC-V CPU delivers a major leap in compute capability, designed for deployment across data center, automotive, and edge applications. Veyron V2 is available as licensable IP for integration into custom SoCs or as a complete silicon platform.

Engineered as a server-class processor, Veyron V2 exceeds the demands of modern, virtualized, cloud-native workloads. Ventana's IP portfolio includes key system-level components such as a RISC-V-compliant IOMMU and supports standard AMBA interfaces, enabling seamless integration with third-party IP and acceleration blocks.

IP available now.

Silicon platforms launching in early 2026.

Key features

Modern Architecture, RVA23-Aligned

- Fully compliant with the RVA23 RISC-V specification

- Comparable PPA to Arm Neoverse V3 / Cortex-X4

- Standard AMBA CHI.E coherent interface for SoC and chiplet integration

- Co-architected with Veyron E2 for seamless vector, AI acceleration, and big-little style heterogeneous compute configurations

Extreme Performance and Power Efficiency

- Optimized for high IPC and 3+ GHz core frequency

- 15-wide out-of-order core: fetch, decode, and execute up to 15 instructions per cycle

- Balanced performance-per-watt architecture optimized to scale from hyperscale to edge environments

- Advanced power gating and DVFS support for fine-grained control

- Up to 32 cores per cluster with decoupled front-end and advanced branch prediction

- High-performance 512-bit RVV 1.0 vector unit with INT8 and BF16 support

- Integrated matrix unit delivering up to 0.5 TOPS/GHz/core (INT8)

- Macro-op caching and aggressive prefetching for instruction and data streams

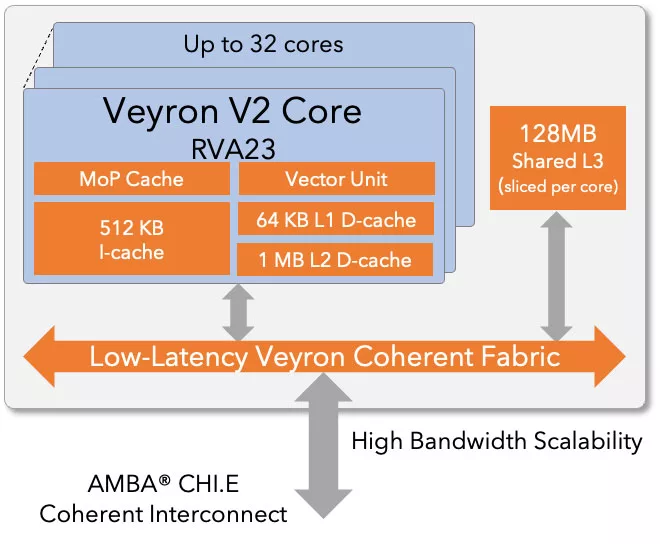

Advanced Cache & Cluster Architecture

- 1.5 MB private L2 cache per core

- Shared L3 cache configurable from 1–4 MB per core (up to 128 MB per cluster)

- Low-latency coherent cluster fabric

- High-bandwidth shared resources optimized for multithreaded workloads

Server-Class Reliability, Virtualization, and Optimization

- Full architectural virtualization support for cloud-native workloads

- Comprehensive RAS:

- ECC on all caches and functional RAMs

- End-to-end data poisoning protection

- Background error scrubbing and logging

- Built-in side-channel attack mitigation

- Comprehensive performance profiling and tuning support

Flexible IP Integration for Custom SoCs

- Clean, portable RTL – no custom macros or proprietary RAMs

- Modular multi-core cluster design for high-core-count scaling

- Integration-ready with standardized IP interface

Modern Architecture, RVA23-Aligned

- Fully compliant with the RVA23 RISC-V specification

- Comparable PPA to Arm Neoverse V3 / Cortex-X4

- Standard AMBA CHI.E coherent interface for SoC and chiplet integration

- Co-architected with Veyron E2 for seamless vector, AI acceleration, and big-little style heterogeneous compute configurations

Extreme Performance and Power Efficiency

- Optimized for high IPC and 3+ GHz core frequency

- 15-wide out-of-order core: fetch, decode, and execute up to 15 instructions per cycle

- Balanced performance-per-watt architecture optimized to scale from hyperscale to edge environments

- Advanced power gating and DVFS support for fine-grained control

- Up to 32 cores per cluster with decoupled front-end and advanced branch prediction

- High-performance 512-bit RVV 1.0 vector unit with INT8 and BF16 support

- Integrated matrix unit delivering up to 0.5 TOPS/GHz/core (INT8)

- Macro-op caching and aggressive prefetching for instruction and data streams

Advanced Cache & Cluster Architecture

- 1.5 MB private L2 cache per core

- Shared L3 cache configurable from 1–4 MB per core (up to 128 MB per cluster)

- Low-latency coherent cluster fabric

- High-bandwidth shared resources optimized for multithreaded workloads

Server-Class Reliability, Virtualization, and Optimization

- Full architectural virtualization support for cloud-native workloads

- Comprehensive RAS:

- ECC on all caches and functional RAMs

- End-to-end data poisoning protection

- Background error scrubbing and logging

- Built-in side-channel attack mitigation

- Comprehensive performance profiling and tuning support

Flexible IP Integration for Custom SoCs

- Clean, portable RTL – no custom macros or proprietary RAMs

- Modular multi-core cluster design for high-core-count scaling

- Integration-ready with standardized IP interface

Chiplet Integration & Packaging

- Standardized chiplet interfaces:

- Ventana D2D multi-protocol controller

- UCIe PHY for chiplet-based system integration

- Compatible with cost-effective organic packaging for volume deployment

- Configurable TDP for deployment across power-performance targets

- Turbo profile management with real-time power behavior control

- Digital power models at both core and cluster level for dynamic scaling

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is High-performance RISC-V CPU?

High-performance RISC-V CPU is a CPU IP core from Ventana Micro Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.