Vendor:

Nextera Video

Category:

Video Transport

SMPTE ST 2110 Core

ST 2110 enables standards based media transport over IP for providing individual packetization of video, audio and metadata.

Overview

ST 2110 enables standards based media transport over IP for providing individual packetization of video, audio and metadata.

Key features

- Supported Codecs (3rd Party)

- TICO

- JPEG2000

- VC-2

- JPEG-XS

- Uncompressed

- 10G/25G/50G/100G

- Video Specs

- 8 - 16 bpp

- 23 - 60 fps (I, P, PSF)

- RGB, YCbCr, Key

- 4:4:4, 4:2:2, 4:2:0

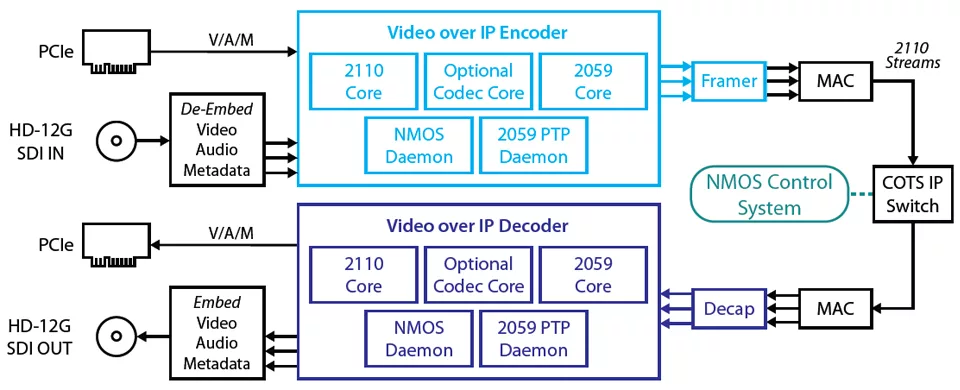

Block Diagram

ST 2110 Core block diagram

Applications

- SDI-IP Gateways

- PCIe Boards

- Media Servers

What’s Included?

- ST 2110-10 - System Timing

- ST 2110-20 - Uncompressed Video Stream

- ST 2110-21 - Traffic Shaping

- ST 2110-30 - Uncompressed Audio Stream

- ST 2110-40 - Ancillary Data (Metadata)

- NMOS IS-04 - Discovery and Registration

- NMOS IS-05 - Connection Management

- 4Kp60 Video Support

- Available as a Xilinx or Altera FPGA Core

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

ST 2110 Core

Vendor

Nextera Video

Provider

Nextera Video

HQ:

USA

Nextera’s goal is to solve challenging problems by developing premium products and solutions for media professionals. Our approach to designing products starts by evaluating the core of real world problems and developing products that are well designed, feature rich, intuitive, and affordable.

The migration to Video over IP is upon us and we are here to ease that transition with an array of solutions, including our Video over IP cores and VIDIO FMC development module. Our VIDIO development module was created specifically to provide an affordable and effective platform on which to develop new 4K and Video over IP products.

We also offer a variety FPGA IP cores supporting the SMPTE ST 2110 and ST 2059 Video over IP standards along with software cores for auto detection and switching of IP signals following the AMWA NMOS specification. We also offer cores for scaling, de-interlacing, noise reduction, image enhancement, frame rate conversion, etc. in both fixed function and running on our programmable video processor core.

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Tfox

Enabling High Performance SoCs Through Multi-Die Re-use

This paper gives a high-level overview of a technique for rapid design of new IC designs using multiple dice packaged in a variety of aggregations allowing for differnent performance levels and price points to be achieved. The technique relies on a new high-bandwidth low pin-count communication channel between two or more dice.

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

This paper presents the interconnect solution adopted for an HDTV SoC developed in HVD division of STM. The SoC is a one-chip satellite HDTV set-top box IC developed in 65nm technology. The interconnect of this HDTV SoC is the first in STM implementing a mixed architecture based on the circuit-switched interconnect named STBus and the new NoC interconnect named VSTNoC.

Steps for Delivering Multimedia Over 5 GHz WLANs

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

The H.264 Scalable Video Codec (SVC) reduces network bandwidth, eliminates transcoding, and simplifies storage management. Here's how it works.

Frequently asked questions about Video Transport IP cores

What is SMPTE ST 2110 Core?

SMPTE ST 2110 Core is a Video Transport IP core from Nextera Video listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.