DDR5 MRDIMM PHY and Controller

-edge IP for high-performance multi-channel memory systems The DDR5 12.8Gbps MRDIMM Gen2 PHY and controller memory IP system solu…

Overview

Leading-edge IP for high-performance multi-channel memory systems

The DDR5 12.8Gbps MRDIMM Gen2 PHY and controller memory IP system solutions double the performance of DDR5 DRAM. The DDDR5 12.8Gbps design and architecture address the need for greater memory bandwidth to accommodate unprecedented AI processing demands in enterprise and data center applications, including AI in the cloud.

The DDR5 MRDIMM Gen2 IP system solution is available today, ready to enable advanced SoCs with flexible floorplan design options, while at the same time, the architecture allows fine-tuning of power and performance based on individual application requirements.

Cadence supports your SoC/IP integration and development with EDA tools, Verification IP (VIP), and Rapid System Bring-Up software.

Key features

PHY

- Includes DDR5 training with write-leveling and data-eye training, and I/O pads with impedance calibration logic and data retention capability

- Programmable per-bit (PVT compensated) deskew on read and write data paths

- RX and TX equalization for heavily loaded systems

- Microcontroller-based PHY-independent advanced training that provides flexibility

- Low latency for data-intensive applications

- Signal integrity, board, and package design guidelines

Controller

- QoS features allow command prioritization on Arm AMBA 4 AXI and CHI interfaces

- Memory controller interface complies with DFI standards up to version 5.1

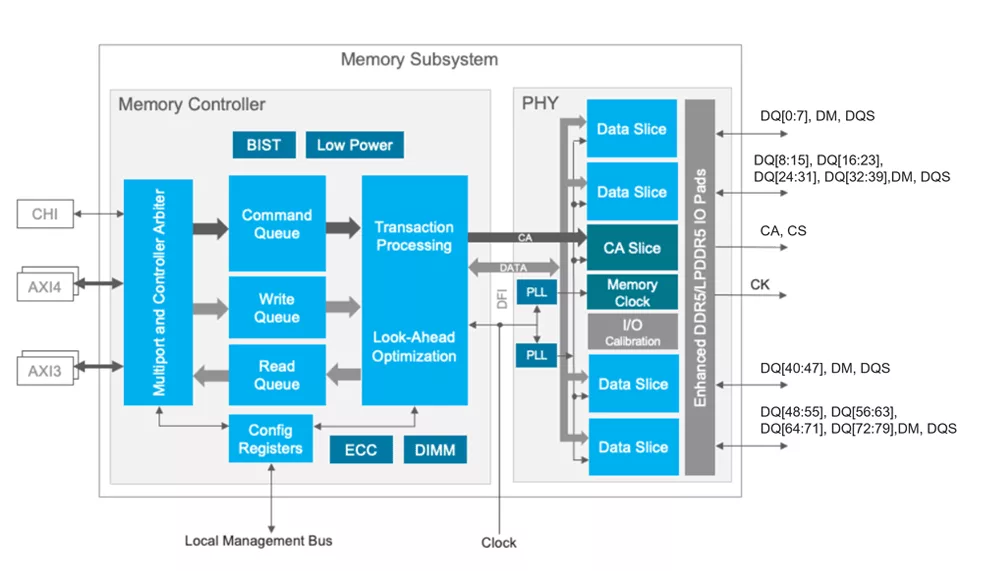

Block Diagram

Benefits

- Scalable: The flexible floorplan design options enable easy integration into advanced SoCs, allowing for scalable solutions that can grow with your needs.

- High Performance: Industry-first Cadence DDR5 12.8Gbps MRDIMM Gen2 PHY and controller doubles the performance of DDR5 DRAM.

- Enhanced Memory Bandwidth: Addresses the need to accommodate AI processing demands in enterprise and data center applications.

- Power and Performance Tuning: The architecture allows fine-tuning of power and performance based on individual application requirements.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Controller IP cores

What is DDR5 MRDIMM PHY and Controller?

DDR5 MRDIMM PHY and Controller is a DDR IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.