DDR5 RDIMM Verification IP

The DDR5 RDIMM Verification IP provides an effective & efficient way to verify the components interfacing with DDR5 RDIMM interfa…

Overview

The DDR5 RDIMM Verification IP provides an effective & efficient way to verify the components interfacing with DDR5 RDIMM interface of an ASIC/FPGA or SoC. The DDR5 RDIMM VIP is fully compliant with Standard DDR5 specification from JEDEC. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key features

- Compliant to JEDEC DDR5 SDRAM & DDR5 RCD Specification.

- Supports connection to any DDR5 Memory Controller IP communicating with a JEDEC compliant DDR5 Memory Model.

- Supports configurable SDRAM addressing of different sizes (x4, x8 and x16).

- Available in all memory sizes from up to 64 Gb.

- Supports all Command Address Rates (SDR1, SDR2 & DDR).

- Supports Output Inversion and Mirroring.

- Supports training modes: DCSTM, QCSTM, DCATM, EDCATM, QCATM.

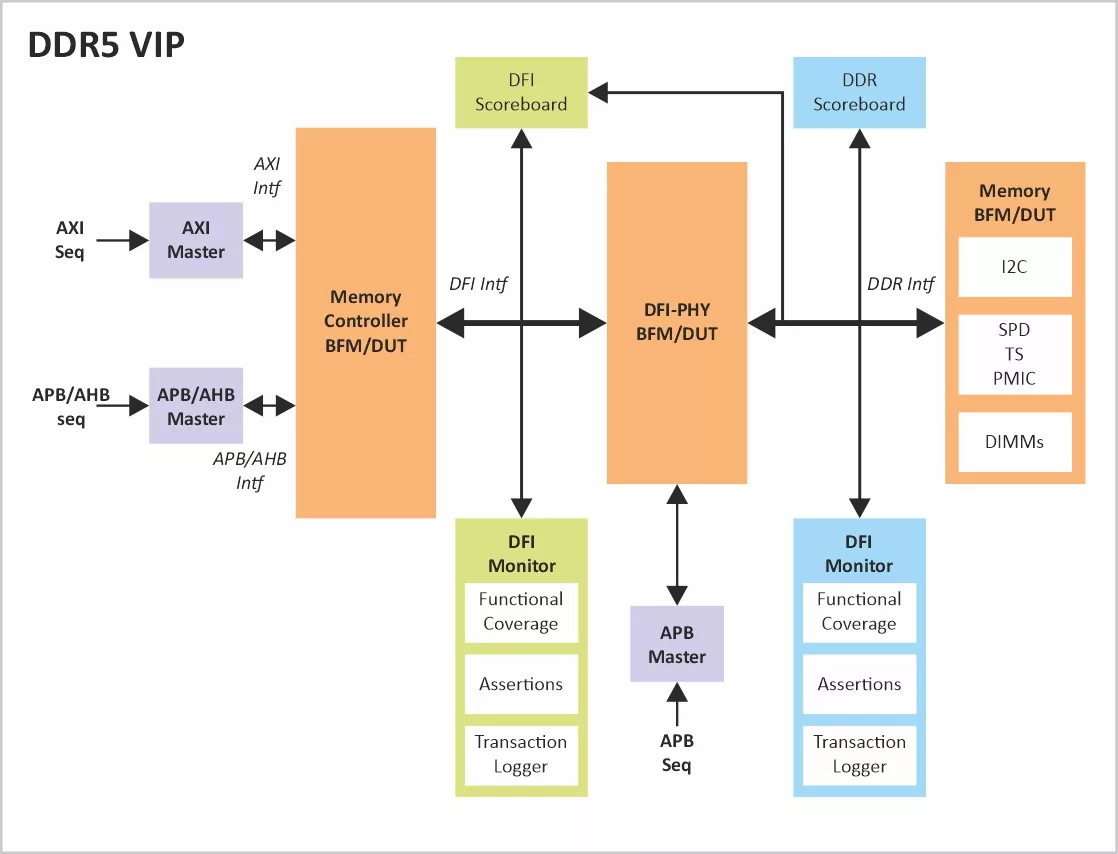

- Supports Transparent Mode, VHost Mode, CA Validation Pass-Through Mode. AXI Seq AXI Master APB/AHB seq APB/AHB Master APB/AHB In DFI In Memory Controller BFM/DUT DFI Monitor Functional Coverage Asser ons Transac on Logger DDR In DFI-PHY BFM/DUT APB Master APB Seq DFI Monitor Functional Coverage Asser ons Transac on Logger Memory BFM/DUT I2C SPD TS PMIC DIMMs

- Supports Control words decode, read, directed and paged access.

- Supports 3DS with command to command timings checks in SLR & DLR.

- Supports Data Masking (DM).

- Supports Cyclic Redundancy Check (CRC).

- Support for all speed-grades/speed-bins.

- Supports Programmable burst lengths (BC8, BL16, BL32, BL32 OTF).

- Supports configurable timing parameters and rank associations.

- Supports capturing all the valid DDR5 commands including Activate, Read Write, Precharge.

- Supports CA parity for command/address bus.

- Supports Power-up Reset and initialization sequences.

- Supports Precharge Power-Down, Active Power-Down, Self-Refresh (with and without Clock Stop) operation.

- Reports various timing errors, which can be used to check any timing violations.

- Provides full control to the user to enable/disable various types of messages.

- Supports full timing models or bus functional models.

- Support for Multiple Ranks architecture.

- Supports advanced System Verilog features like constrained random testing.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Monitor, Controller and Memory Model BFMs.

- Graphical analyzer to show transactions for easy debugging.

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure highest levels of quality.

- 24X5 customer support & response under 90 Min.

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide complete solution and easy

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Interface IP

What is DDR5 RDIMM Verification IP?

DDR5 RDIMM Verification IP is a DDR IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.