112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation

The 112G Ethernet PHY IP, an integral part of the 400GbE/800GbE Ethernet solution enables long reach (LR), medium reach (MR), ver…

Overview

The 112G Ethernet PHY IP, an integral part of the 400GbE/800GbE Ethernet solution enables long reach (LR), medium reach (MR), very short reach (VSR) electrical channels and CEI-112G-Linear, and CEI-112G-XSR+ optical interfaces. The 112G LR-Max PHY surpasses the performance targets of 112G-LR specification further extending channel reach in High Performance Compute applications.

The silicon-proven IP enables up to 800GbE hyperscale data center, networking, AI, pluggable optical module and Ethernet switch SoCs requiring high bandwidth and low latency.

112G LR-Max PHY

Using leading-edge analog mixed-signal design and advanced digital signal processing technologies, the 112G LR-Max PHY IP provides additional margins to the CEI-112G LR specification and provides three orders of magnitude better bit error rate compared to the spec for 45dB channels.

112G LR PHY

The power efficient PHY offers orders of magnitude better BER performance for Long Reach chip to chip channels with two connecters and multiple media. The PHYs’ flexible layout maximizes bandwidth per die-edge by allowing the placement of square macros in a multi-row structure and along all edges of the die. Support for the Pulse-Amplitude Modulation 4-Level (PAM-4), Non- Return-to-Zero (NRZ) signaling, and independent, per-lane data rates allows ultimate flexibility to address a broad range of protocols and applications.

112G VSR PHY

Architected for very short reach chip-to-chip or chip-to-module electrical channels, the ultra-low power 112G VSR PHY enables power efficient pluggable and near packaged 400GbE/800GbE electro-optical interfaces. Combined with Synopsys' routing feasibility study, packages substrate guidelines, signal and power integrity models, and thorough crosstalk analysis, Synopsys provides a comprehensive 112G Ethernet PHY IP products for fast and reliable SoC integration.

Key features

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

- Provides comprehensive 200G/400G/800G solution with routing feasibility study, packages substrate guidelines, signal and power integrity models, and thorough crosstalk analysis

- LR, MR and VSR: DAC-based PAM-4 transmitter includes feed forward equalization (FFE)

- LR, MR and VSR: Digital-based receiver consists of analog front-end (AFE), ADC, and digital signal processor (DSP)

- High-performance receive equalization supporting required channel loss

- Continuous calibration and adaptation (CCA) algorithms provide robust performance across process, voltage, and temperature variations

- Low jitter phase-locked loops (PLLs) provide robust timing recovery and better jitter performance

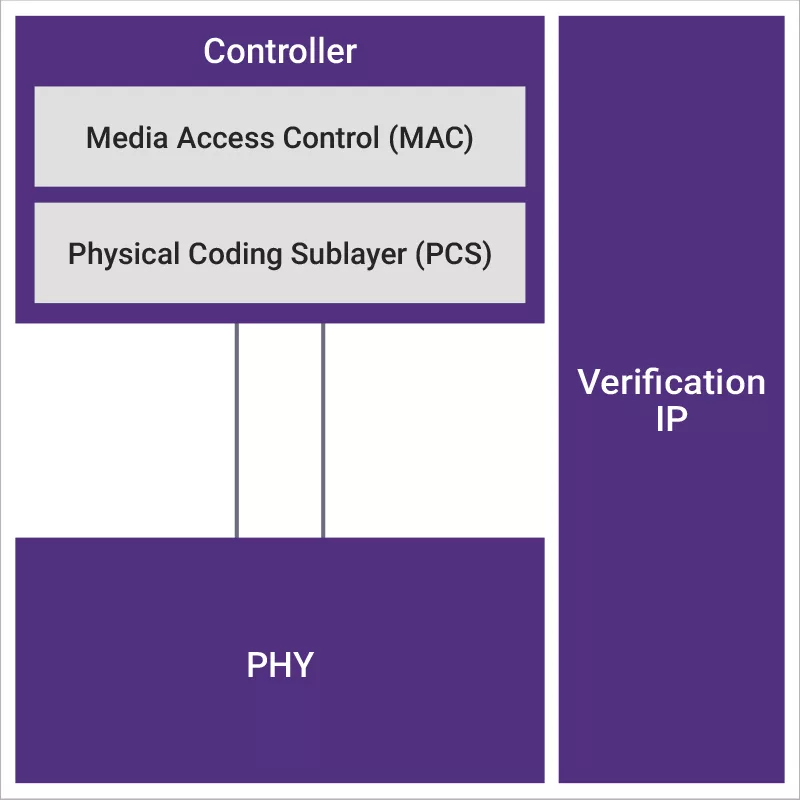

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 6nm | N6 | — |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is 112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation?

112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation is a Single-Protocol PHY IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.