Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

The MIPS® P8700 Multiprocessing System is the first RV64GCZba_Zbb compliant CPU IP focused on high performance, data movement and…

Overview

The MIPS® P8700 Multiprocessing System is the first RV64GCZba_Zbb compliant CPU IP focused on high performance, data movement and latency-intensive Automotive applications. In addition to implementing the RV64GC RISC-V ISA, the MIPS P8700 also implements proven features from the MIPS ISA, to enhance performance and functionality for automotive and embedded applications.

The MIPS P8700 is built on proven MIPS micro architecture deployed in more than 28 car models across global OEMs. As such, the P8700 MPS provides best in class multi-core performance for use in system-on-chip (SoC) applications. The P8700 combines a deep pipeline with multi-issue Out-Of Order-execution and multi-threading to deliver outstanding computational throughput.

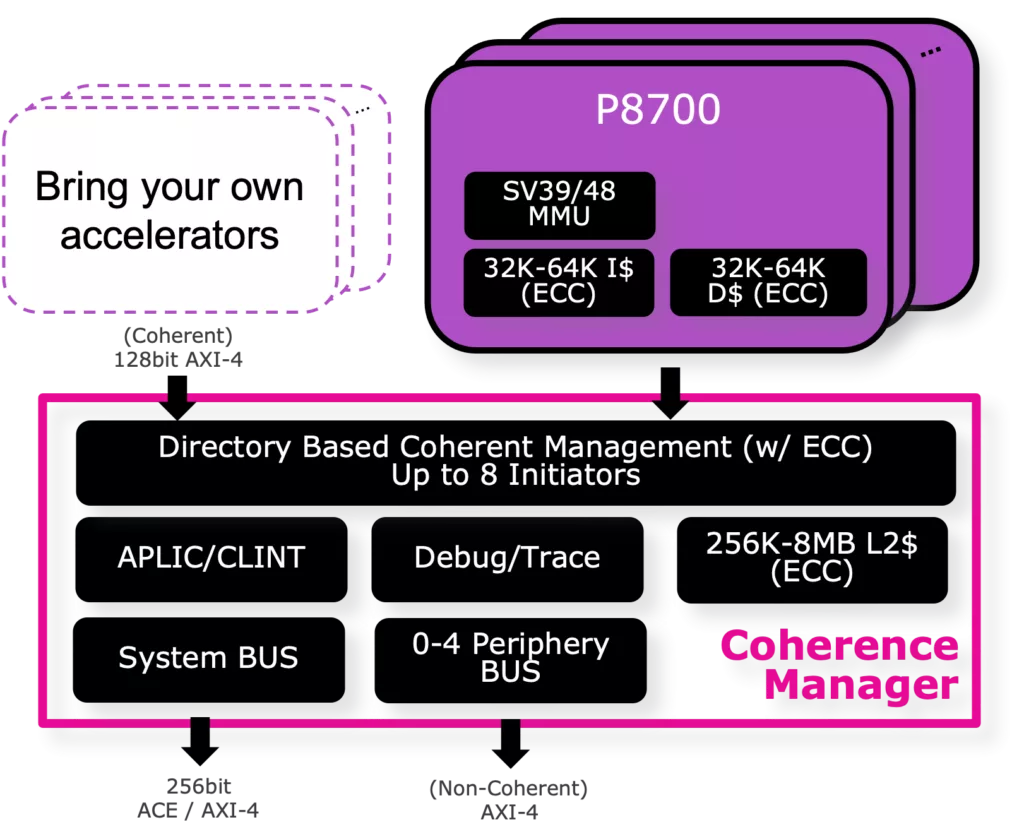

The P8700 Coherence Manager maintains Level 2 (L2) cache and system level coherency between all cores, main memory, and I/O devices. The P8700 is a configurable and a synthesizable solution. P8700 clusters can be configured with a variable number of cores, I/O coherent interfaces, and L2 cache size. The MIPS P8700 cores can be configured to meet different application requirements with options for Level 1 (L1) cache sizes, and support for 1 or 2 hardware threads.

The MIPS Coherence Manager has an AMBA® ACE interface that enables the P8700 Multiprocessing System to coherently scale up to 64 heterogeneous clusters at the system-on-chip (SoC) level with each cluster supporting of up to 6x P8700 cores each, with up to 2 hardware threads per core.ation with heterogeneous CPU clusters and other accelerators at the system-on-chip (SoC) level.

Each P8700 core implements the RISC-V RV64GC Instruction Set Architecture (ISA) with full hardware multi-threading.

Key features

- The only Multi-Threaded Out-of-Order RISC-V Core with ASIL-B Certification

- Highly scalable multi-core, multi-cluster, coherent computing solution

- MIPS extensions for improved performance and functionality

- Use in Automotive, Datacenter, and Embedded applications

Block Diagram

Benefits

- High-performance 64-bit RISC-V application processor

- 2-way simultaneous multi-threading

- ASIL-B capable safety element out context

- Tightly-coupled accelerator interfaces

- Custom built for automotive compute solutions

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs?

Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs is a CPU IP core from MIPS listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.