64-bit High Performance Out-of-Order Processor - Out-of-Order, 3/4/6-Wide Decode

The UX1000 Series have three different variants: UX1030, UX1040 and UX1060.

Overview

The UX1000 Series have three different variants: UX1030, UX1040 and UX1060. UX1030 is a 3-wide processor with good performance and smaller power & area; UX1040 is a 4-wide processor with better performance and balanced power & area; UX1060 is a 6-wide processor with even higher performance targeting high-end applications.

1000 Series Performance and Configurability

| Highlights of UX1000 Processor | |||

| Pipeline | Out-of-Order 12-pipeline | ||

| Decode Width | Configurable 3, 4 or 6-wide decode | ||

| Issue-Width | Configurable up to 8 integer instructions and 3 vector instructions | ||

| Privilege Modes | Machine, Supervisor, User | ||

| ISA | RV64IMAFDCVBZfh | ||

| Bit Manipulation | Zba + Zbb + Zbc + Zbs | ||

| Floating Point | Zfh(Half precision), F (Single precision) and D(Double precision) | ||

| Vector Extension | RISC-V Vector 1.0 Version (Up to Date) | ||

| Memory Addressing | Virtual addressing Sv39, Sv48 | ||

| Instruction Subsystem | Instruction Cache , ILM, Private L2 Cache, Cluster Cache | ||

| Data Subsystem | Data Cache, DLM , Private L2 Cache, Cluster Cache | ||

| SoC Connectivity | AXI Mem Bus, AHB-Lite Peripheral Bus, AXI Slave Port, AXI IO Coherence Port | ||

| Multi-core Configurations | Support single cluster and multi-cluster configuration, each cluster can have up to 8 cores | ||

Key features

1000 Series Configurable Pipeline Diagram.

- Cutting-Edge Pipeline and Micro-Architecture Design

- UX1000 Series have three variants configurations: UX1030, UX1040 and UX1060.

- UX1030:3-wide decode

- Good performance with smaller power & area.

- UX1040:4-wide decode

- Better performance with balanced power & area.

- UX1060:6-wide decode

- Even higher performance targeting high-end applications.

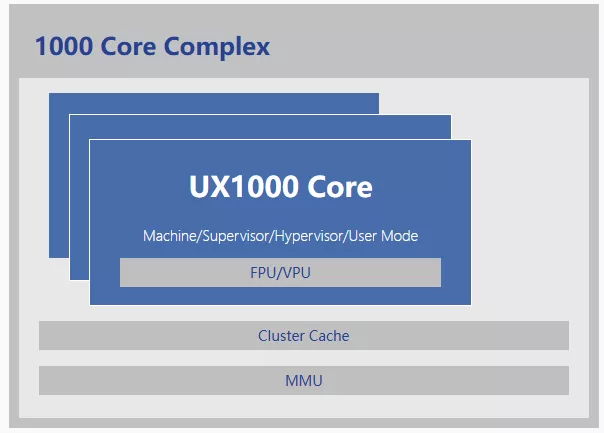

1000 Series Single Cluster Configuration Features.

- Single Core Configuration Features:

- RISC-V RV64IMACFDVBZfh ISA supported.

- Configurable 3, 4 or 6-wide decode, out-of-order Pipeline.

- Full Vector Extension with configurable VLEN & DLEN.

- Double, Single and Half-Precision floating point.

- Configurable ICache, DCache, ILM and DLM with ECC.

- Cluster Configuration Features:

- Up to 8 SMP cores in one Cluster with Cache Coherency.

- Configurable Private L2 cache + Cluster Cache .

- Configurable IO Coherency Ports.

- Configurable Cluster Cache with SECDED ECC.

- Configurable CLM partition for deterministic data access in Cluster Cache with 128-b CLM port.

- Configurable Dual-Mode feature (Real-Time & Application).

1000 Series Multi-Cluster Configuration Features

- Each Cluster supports up to 16 cores.

- Each core can be configured with Private Cluster Cache.

- Nuclei-CCI:

- Nuclei developed Cross-Bar based Coherent interconnect for Multi-Cluster.

- Support System Level Cache.

- Nuclei-NoC:

Nuclei developed Non-Coherent Mesh-NoC based bus fabric. - Heterogeneous Multi-Cluster Mode

- Different clusters (UX1060, UX1040, or UX1030) can be combined into one subsystem.

- Support up to 8 Clusters in a subsystem.

Block Diagram

Benefits

- Real-time Feature

- RV64I MAFDCVBZfh

- 12-Stage Pipeline

- I/D Cache

- Machine, Supervisor User Mode,Hypervisor

- Security(PMP, TEE)

- NICE Extension

- AXI system bus

- RISC-V Standard Debug

- JTAG & 2-wire JTAG

- Low Latency Interrupt

- Full Dev Kit & SDK

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 64-bit High Performance Out-of-Order Processor - Out-of-Order, 3/4/6-Wide Decode?

64-bit High Performance Out-of-Order Processor - Out-of-Order, 3/4/6-Wide Decode is a CPU IP core from Nuclei System Technology listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.