32Gbps SerDes IP in TSMC 22nm ULP

The relentless demand for higher data throughput in data centers and high-performance computing (HPC) systems drives the need for…

Overview

The relentless demand for higher data throughput in data centers and high-performance computing (HPC) systems drives the need for ultra-high-speed signaling with minimal latency. AionChip’s Argos SerDes IP is purpose-built to meet these demands, delivering exceptional signaling bandwidth with industry-leading latency performance.

Leveraging a proven high-speed SerDes architecture, Argos SerDes achieves an optimal balance of latency, power, and area efficiency—without compromising on performance. Its flexible multi-rate design supports data rates from 1.25Gbps to 32Gbps, ensuring full backward compatibility and seamless integration into next- generation systems.

Key features

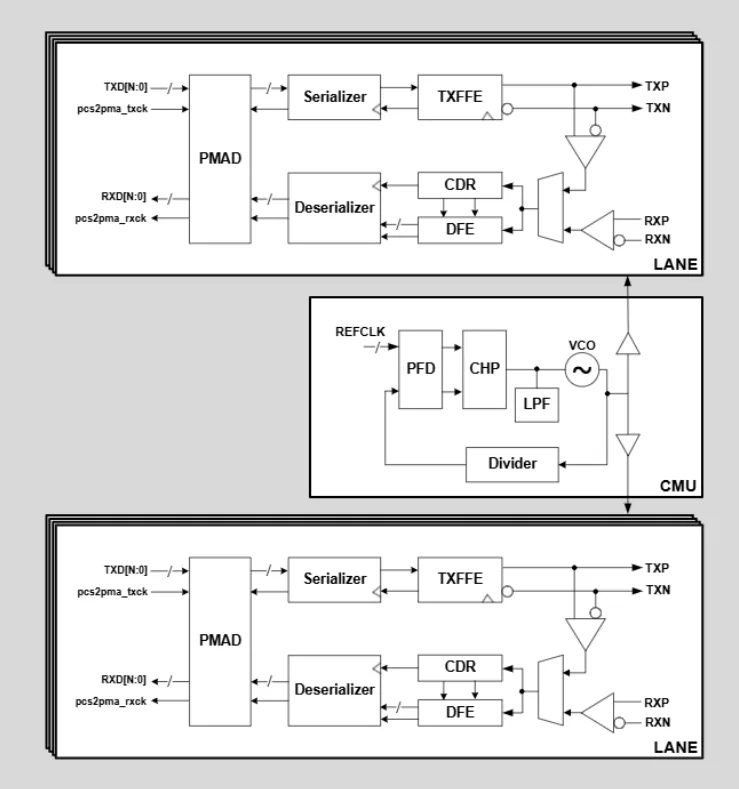

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Configurable low latency parallel data interface for optimal system performance

- Broad protocol compatibility including PCIe Gen1–5, Ethernet (1G/10G/25G/50G/100G), JESD204B/C, CPRI, and many other high-speed serial standards

- Adaptive RX EQ combining CTLE + 10-Tap DFE

- Programmable 4-Tap TX FFE with output swing control

- Non-intrusive Eye monitor for real-time signal quality observation

- Comprehensive loopback modes: TX-to-RX, RX- to-TX, Line-side and System-side

- Low-Power Standby State support for energy- efficient operation

- Built-in test and debug features including PRBS Generators and Checkers, AC-JTAG (1149.6), analog debug port

Block Diagram

What’s Included?

- Standard integration views: LEF abstract view, .LIB timing view, Verilog model, DRC, LVS, ANT reports, and GDSII

- Synthesizable soft RTL with SDC and synthesis script

- Documentations: Datasheet, Integration guide, and Programming guide

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 22nm | ULP | — |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 32Gbps SerDes IP in TSMC 22nm ULP?

32Gbps SerDes IP in TSMC 22nm ULP is a Multi-Protocol PHY IP core from AionChip Technologies listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.