112G Multi-Rate SerDes

Empowering customers to thrive in the AI Era, INNOSILICON™ introduces its most 112G SerDes (Serializer/Deserializer) and Controll…

Overview

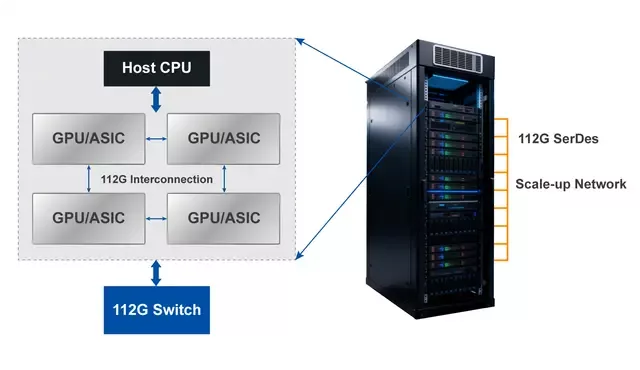

Empowering customers to thrive in the AI Era, INNOSILICON™ introduces its most advanced 112G SerDes (Serializer/Deserializer) and Controller IP, designed to meet the high-performance interconnect demands of cutting-edge computing chips in hyperscale data centers, cloud training and inference clusters, and next-generation networking infrastructure. This solution delivers 200Gbps, 400Gbps, and 800Gbps interconnect bandwidth and supports both short- and long-reach, including optical interconnect applications.

Designed with a small footprint, ultra-low latency, and low power consumption, the INNOSILICON™ 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO). Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.

Key features

- Fault detection capable of identifying conditions that compromise link reliability (e.g., loss of synchronization or high bit error rates)

- Pseudo-random test-pattern generator and checker for both transmitter and receiver testing

- Implements Reed-Solomon Forward Error Correction (RS-FEC) using the RS (544,514) code with codeword interleaving as defined in IEEE 802.3

- RS-FEC supports external statistics collection by providing a statistics vector

- Supports evolving IEEE standards as specified by the UALink Consortium

- Multi-rate support and configurable for 400G and 200G application

- High-speed PMA service interface operates at 106.25Gbps per lane

- Features auto-negotiation and link training capabilities

- High-performance receive equalization with channel loss of 35 dB

- Continuous Calibration and Adaptation (CCA), providing robust performance across voltage and temperature variations

- Adaptive and configurable RX Continuous Time Linear Equalizer (CTLE), Feed Forward Equalizer (FFE), and Decision Feedback Equalizer (DFE)

- Locked Loop (PLL) provides robust timing recovery and better jitter performance

- Advanced, built-in diagnostics of hard macro functions through eye scope

- Embedded pseudo-random bit sequence (PRBS) for internal and external loopbacks

- Integrated microcontroller and Firmware to manage PHY configuration

- Embedded temperature sensor for on-die temperature measurements

Block Diagram

Benefits

- AI Era-ready performance: higher data rates, lower power consumption, smaller area, and robust link reliability.

- Flexible harden IP delivery options to accelerate integration and reduce customer costs.

- Advanced packaging and PCB co-design to fully unlock IP performance and stability.

- Comprehensive support from design through mass-production bring-up, ensuring worry-free and timely service quality.

What’s Included?

- Verilog Sim Behavioral simulation model for the PHY

- Encrypted IO spice netlist for SI evaluation

- Integration Guide

- Databook

- Test Guide

- GDSII Layout and layer map for foundry merge

- LIB and LEF

- LVS and DRC verification reports

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 112G Multi-Rate SerDes?

112G Multi-Rate SerDes is a Multi-Protocol PHY IP core from Innosilicon Technology Ltd listed on Semi IP Hub.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.