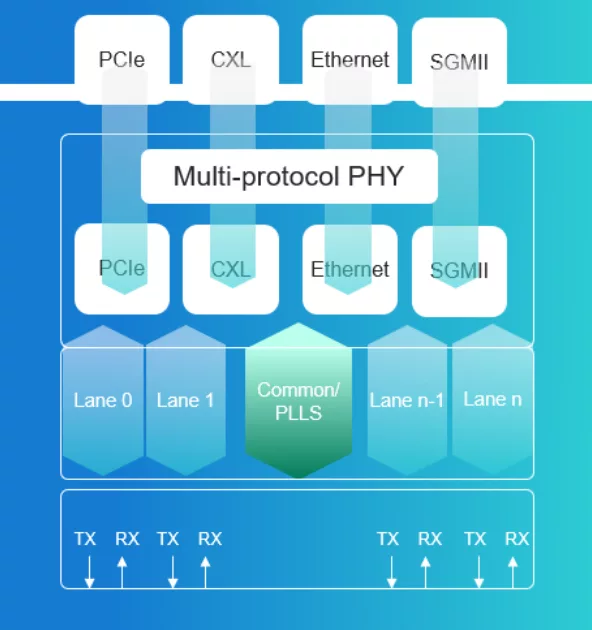

Learn more about Multi-Protocol PHY IP core

Morgan State University (MSU) recently received an Apple Innovation Grant, designed to support engineering schools as they develop their silicon and hardware technologies. The New Silicon Initiative (NSI) is designed to inspire and prepare students for careers in hardware engineering, computer architecture, and silicon chip design.

Increasingly, more of the focus on mobile has centered around cloud datacenters and the networking to get the data back and forth between these datacenters and the mobile device. Functions like voice recognition and mapping depend on the ability to split the functionality between the smartphone, for local processing like encryption and compression, and the back end, where a large number of servers can do the heavier lifting before returning the results.

Steven Brown

The Cadence 10G multi-protocol PHY was architected to address this exact challenge. Designed to scale across multiple process nodes, it consolidates PCI Express (PCIe), USB, DisplayPort, Ethernet, and other interfaces into a single, compact, silicon-efficient block. What sets it apart is simultaneous multi-protocol support, which enables multiple data paths without duplicating hardware, requiring extra board connectors, or paying the area and power penalty of separate IP blocks.