100G SerDes PAM4 PHY

The SERDES PHY IP delivers a high-performance, low-power solution for high-speed interfaces up to 112Gbps.

Overview

The SERDES PHY IP delivers a high-performance, low-power solution for high-speed interfaces up to 112Gbps. It supports diverse applications including AI accelerators, data centers, 5G infrastructure, and automotive SoCs.

The Ethernet PHY IP is optimized for CEI-112G and supports 8b/10b encoding for Gen1/Gen2 and 128b/130b for Gen3/Gen4, ensuring accurate serialization and deserialization of data streams.

With robust equalization and proven interoperability, it maintains high signal integrity across lossy channels and is well-suited for advanced SoC integration.

Key features

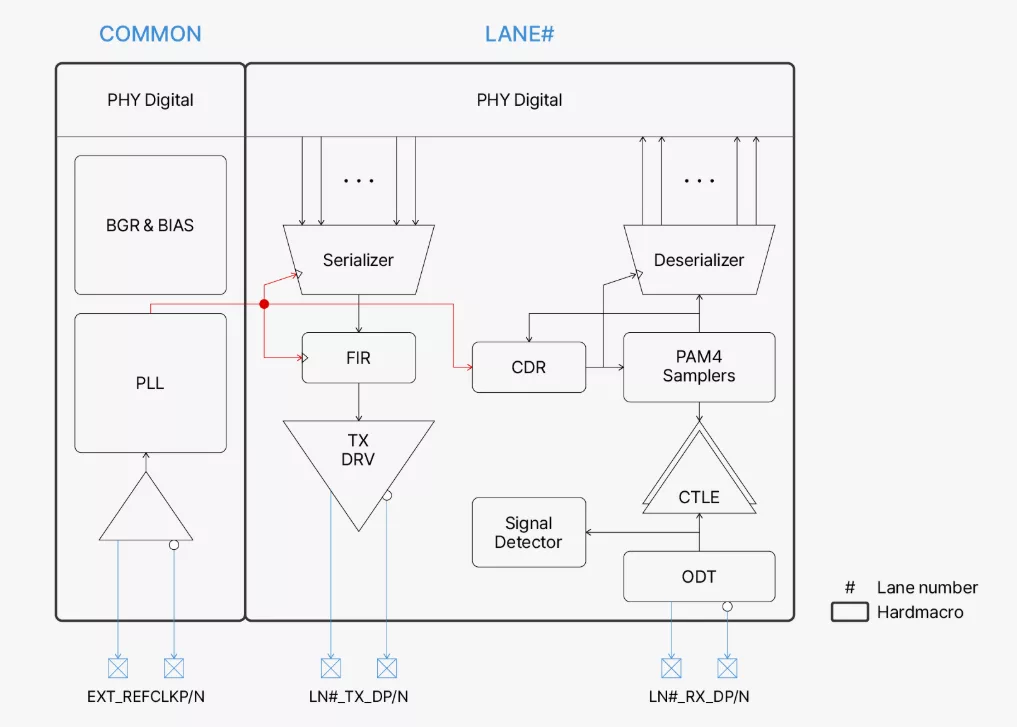

- Transmit Path:

- Accepts four 10-bit transmit characters (8b/10b) or four 8-bit data blocks (128b/130b)

- Serializes data to differential outputs (TXP/TXN) at up to 16.0Gb/s per lane

- Receive Path:

- Samples incoming serial data from differential inputs (RXP/RXN)

- Deserializes into four 10-bit (8b/10b) or 8-bit (128b/130b) received characters

- Optimized for high-speed Ethernet, PCIe, and custom protocol applications

- Integrated with robust equalization and low-jitter clock recovery for enhanced signal integrity

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 100G SerDes PAM4 PHY?

100G SerDes PAM4 PHY is a Multi-Protocol PHY IP core from Qualitas Semiconductor listed on Semi IP Hub.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.