32Gbps SerDes PHY in GF 22nm

A 32Gbps SerDes PHY in GlobalFoundries 22FDX withlow-jitter, half-rate tran mission, and a configurable CTLE-based receiver.

Overview

A 32Gbps SerDes PHY in GlobalFoundries 22FDX withlow-jitter, half-rate tran mission, and a configurable CTLE-based receiver.

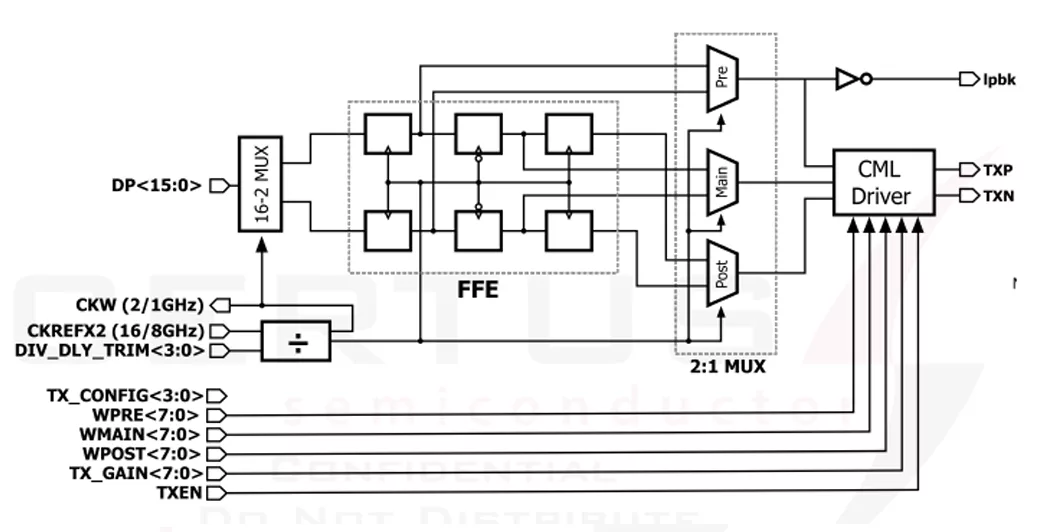

This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs. The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation. The design emphasizes observability and manual configurability, exposing trim controls and monitoring capabilities to support bring-up, characterization, and production test. The SerDes is optimized for integration in GF 22FDX using 0.8V core devices and a high-performance BEOL stack. The design is currently in pre-silicon validation, with tapeout planned.

Library Summary

- Process: GlobalFoundries 22FDX

- BEOL: 1P9M_2Mx_5Cx_1Jx_1Ox_LB

- PDK: GF 22FDX-EXT

- Clocking: On-chip clock multiplier for 8 GHz-> 16 GHz operation

- TX Interface: 16-bit parallel input-> differential serial output

- RX Interface: Differential serial input-> 16-bit parallel output (word clock provided)

- Equalization: TX 3-tap FFE (pre/main/post); RX CTLE with DC + HF gain controls

Operating Conditions

| Parameter | Value |

| Line Rate | 16Gbps / 32Gbps (per lane) |

| Reference Clock | 8 Ghz differential reference |

| Core VDD | 0.8V (0.72V-0.88V) |

| RX Analog Supply | 1.8V (receiver analog rail) |

| Signaling | Differential CML at pads (TX) |

Key features

- Upto 32Gbps per lane with 16Gbps support

- Half-rate TX architecture to reduce internal clock fre quency while maintaining throughput

- Configurable RX CTLE with independent DC gain and HF peaking control

- Digital CDR with configurable loop parameters

- Observability fo bring-up and production

- Protocol-agnostic PHY suitable for a range of serial link implementations

Block Diagram

Applications

- High-speeddataconverter interfaces (e.g. JESD204B/C style links)

- Radar, defense, and real-time signal processing back planes

- Test measurementandhigh-speedinstrumentation links

- Proprietary chip-on-chip / module-to-module serial in terconnects

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 22nm | FDX | — |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 32Gbps SerDes PHY in GF 22nm?

32Gbps SerDes PHY in GF 22nm is a Multi-Protocol PHY IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for globalfoundries.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.