VolTune: A Fine-Grained Runtime Voltage Control Architecture for FPGA Systems

By Akram Ben Ahmed, Takahiro Hirofuchi, Takaaki Fukai

Intelligent Platforms Research Institute, National Institute of Advanced Industrial Sciences and Technology, Tokyo, Japan

Abstract

The rapid emergence of edge computing platforms and large-scale data centers has made power efficiency a primary design constraint, particularly for data-intensive and AI-driven workloads. Field-programmable gate arrays (FPGAs) are increasingly adopted due to their flexibility and potential for energy-efficient acceleration. However, FPGA supply voltages are typically fixed at design time using conservative margins, limiting the ability to adapt power consumption to runtime conditions.

The rapid emergence of edge computing platforms and large-scale data centers has made power efficiency a primary design constraint, particularly for data-intensive and AI-driven workloads. Field-programmable gate arrays (FPGAs) are increasingly adopted due to their flexibility and potential for energy-efficient acceleration. However, FPGA supply voltages are typically fixed at design time using conservative margins, limiting the ability to adapt power consumption to runtime conditions.

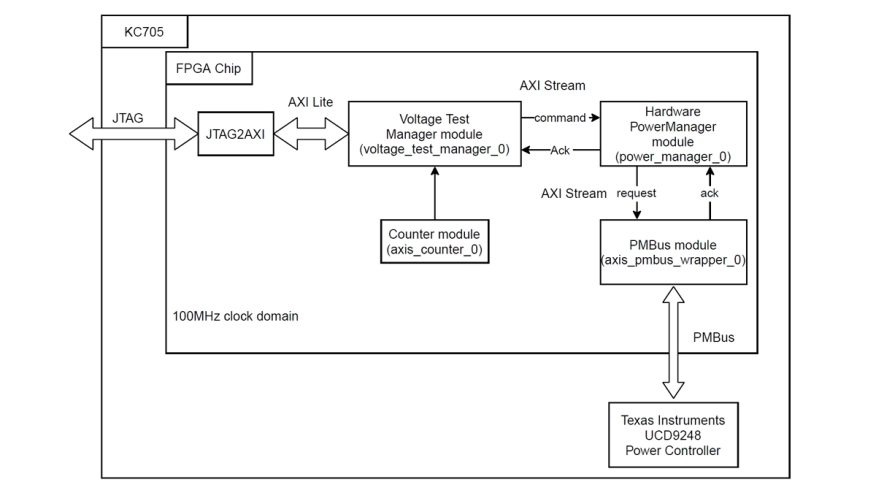

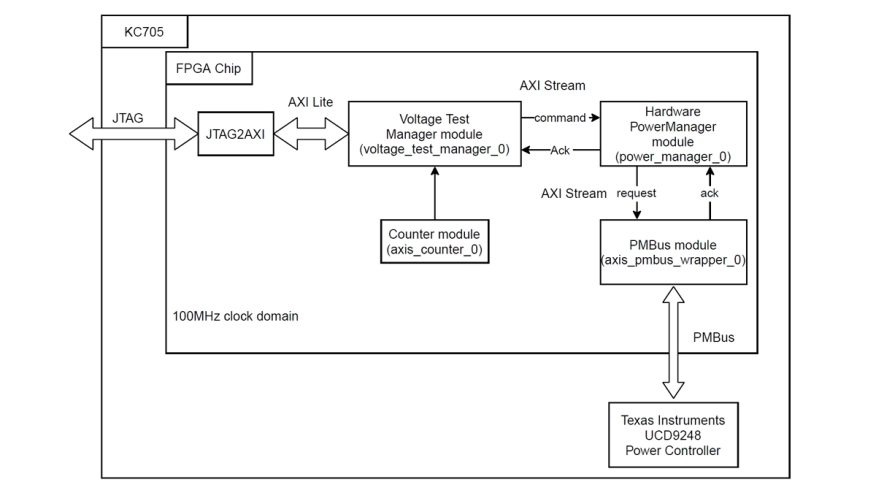

This paper presents VolTune, an open-source runtime voltage control architecture that enables runtime tuning of FPGA supply voltages through FPGA-integrated control logic that abstracts low-level PMBus operations. VolTune provides both hardware-based and software-based control paths, allowing designers to balance deterministic low-latency operation against programmability.

In the presented prototype, the hardware-based control path achieves a measured end-to-end voltage transition latency of 2.3 ms, while the controller adds under 2% static power overhead and under 2% FPGA resource overhead. As a representative case study, VolTune is evaluated on the GTX transceiver supply rail of a Kintex-7 platform. The results show that runtime voltage tuning exposes a bounded operating region with clear trade-offs between energy efficiency and reliability, and achieves up to approximately 29.3% rail-power reduction at 10.0 Gbps when allowing BER up to 10e-6. These results show that FPGA-integrated runtime voltage control can provide practical energy savings with low integration overhead.

To read the full article, click here

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related Articles

- SynapticCore-X: A Modular Neural Processing Architecture for Low-Cost FPGA Acceleration

- A Direct Memory Access Controller (DMAC) for Irregular Data Transfers on RISC-V Linux Systems

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Interstellar: Fully Partitioned and Efficient Security Monitoring Hardware Near a Processor Core for Protecting Systems against Attacks on Privileged Software

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks