RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

By Nick Andreasyan 1, Mikhail Struve 1, Alexey Popov 2, Maksim Nikolaev 2, Vadim Vashkelis 2

1 Automotive Safety Lab

2 Embedded Intelligence Lab

Abstract

RISC-V is emerging as a viable platform for automotive-grade embedded computing, with recent ISO 26262 ASIL-D certifications of commercial RISC-V processor IP demonstrating readiness for safety-critical deployment in autonomous driving systems. However, functional safety in automotive systems is fundamentally a certification problem rather than a processor problem: the dominant costs arise from diagnostic coverage analysis, toolchain qualification, fault injection campaigns, safety- case generation, and compliance with ISO 26262, ISO 21448 (SOTIF), and ISO/SAE 21434.

RISC-V is emerging as a viable platform for automotive-grade embedded computing, with recent ISO 26262 ASIL-D certifications of commercial RISC-V processor IP demonstrating readiness for safety-critical deployment in autonomous driving systems. However, functional safety in automotive systems is fundamentally a certification problem rather than a processor problem: the dominant costs arise from diagnostic coverage analysis, toolchain qualification, fault injection campaigns, safety- case generation, and compliance with ISO 26262, ISO 21448 (SOTIF), and ISO/SAE 21434.

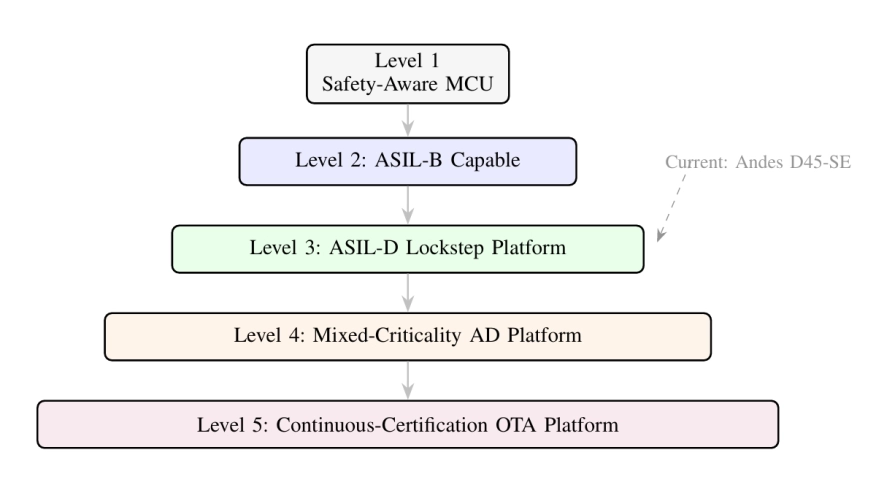

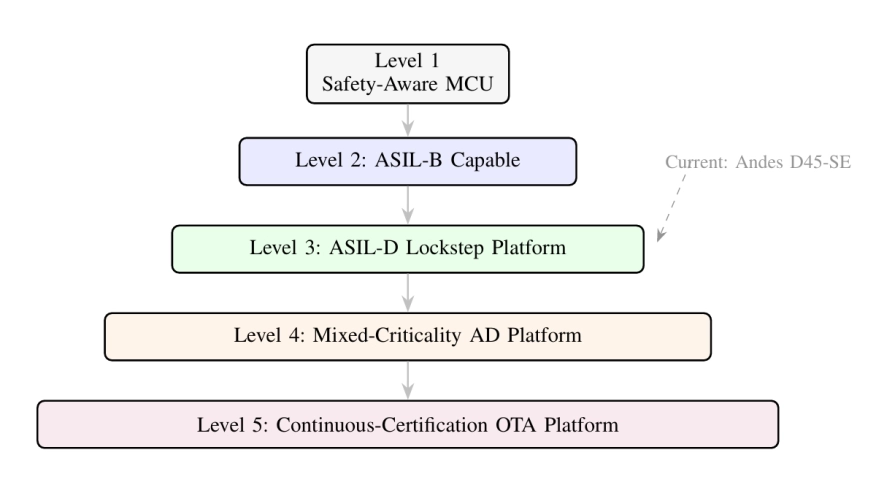

This paper provides a structured analytical framework and expert-driven research roadmap for enabling economically superior certification of automotive-grade RISC-V platforms. Rather than proposing a single algorithmic breakthrough, we contribute: (1) a certification economics framework with formal cost and advantage models for strategic decision support; (2) an ML assisted certification framework mapping LLMs, knowledge graphs, reinforcement learning, and graph neural networks to specific certification bottlenecks; (3) a five-level RISC-V Safety Maturity Model (RSMM) for evaluating platform certifiability; and (4) an illustrative case study applying the framework to an ASIL-D autonomous emergency braking (AEB) ECU.

We present a structured comparison of Arm and RISC-V architectures across eight functional safety dimensions, address the convergence of ISO 26262, ISO 21448, and ISO/SAE 21434 for autonomous driving, and define quantitative evaluation metrics for certification cost reduction. The paper is positioned as an analytical perspective contribution that structures the research space and identifies the highest-value problems for the RISC-V automotive certification ecosystem.

Index Terms: RISC-V, Functional Safety, ISO 26262, SOTIF, Autonomous Driving, ASIL-D, Certification Economics, Machine Learning, Safety Case Automation, FMEDA, Toolchain Qualification

To read the full article, click here

Related Semiconductor IP

- 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- Configurable CPU tailored precisely to your needs

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- Multi-core capable 32-bit RISC-V CPU with vector extensions

- Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

Related Articles

- CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

- A RISC-V Multicore and GPU SoC Platform with a Qualifiable Software Stack for Safety Critical Systems

- Efficient Hardware-Assisted Heap Memory Safety for Embedded RISC-V Systems

- The Functional Safety Imperative in Automotive Design

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks