TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks

By Marco Bertuletti 1, Yichao Zhang 1, Diyou Shen 1, Alessandro Vanelli-Coralli 1,2, Frank K. Gürkaynak 1, Luca Benini 1,2

1 Integrated Systems Laboratory (IIS), Eidegenossische Technische Hochschule (ETH), Zurich, Switzerland

2 University of Bologna, Bologna, Italy, and with ETH

Abstract

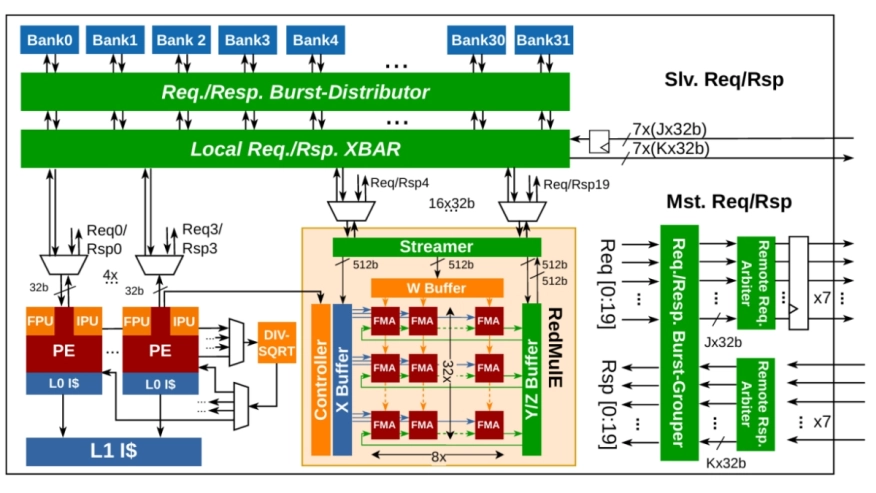

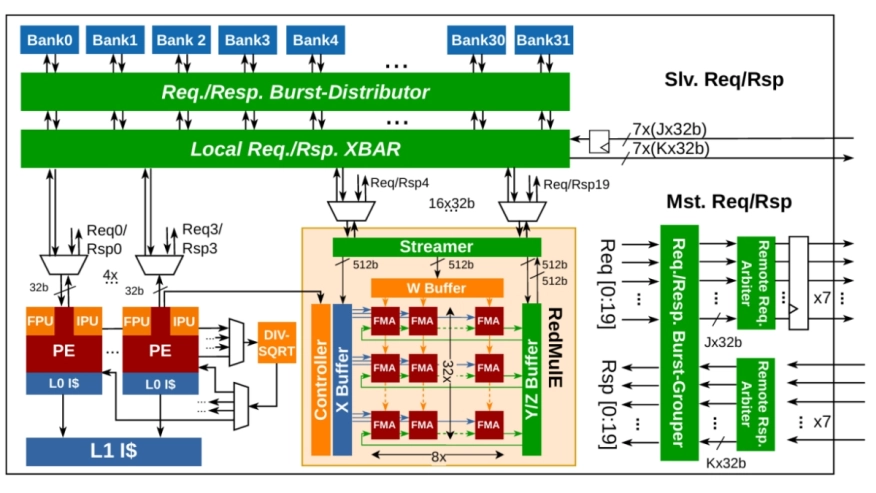

The upcoming integration of AI in the physical layer (PHY) of 6G radio access networks (RAN) will enable a higher quality of service in challenging transmission scenarios. However, deeply optimized AI-Native PHY models impose higher computational complexity compared to conventional baseband, challenging deployment under the sub-msec real-time constraints typical of modern PHYs. Additionally, following the extension to terahertz carriers, the upcoming densification of 6G cell-sites further limits the power consumption of base stations, constraining the budget available for compute (≤ 100 W). The desired flexibility to ensure long term sustainability and the imperative energy efficiency gains on the high-throughput tensor computations dominating AI-Native PHYs can be achieved by domain-specialization of many-core programmable baseband processors. Following the domain-specialization strategy, we present TensorPool, a cluster of 256 RISCV32IMAF programmable cores, accelerated by 16 256 MACs/cycle (FP16) tensor engines with low-latency access to 4MiB of L1 scratchpad for maximal data-reuse. Implemented in TSMC’s N7, TensorPool achieves 3643 MACs/cycle (89% tensor unit utilization) on tensor operations for AI-RAN, 6× more than a core-only cluster without tensor acceleration, while simultaneously improving GOPS/W/mm2 efficiency by 9.1×. Further, we show that 3D-stacking the computing blocks of TensorPool to better unfold the tensor engines to L1-memory routing provides 2.32× footprint improvement with no frequency degradation, compared to a 2D implementation.

The upcoming integration of AI in the physical layer (PHY) of 6G radio access networks (RAN) will enable a higher quality of service in challenging transmission scenarios. However, deeply optimized AI-Native PHY models impose higher computational complexity compared to conventional baseband, challenging deployment under the sub-msec real-time constraints typical of modern PHYs. Additionally, following the extension to terahertz carriers, the upcoming densification of 6G cell-sites further limits the power consumption of base stations, constraining the budget available for compute (≤ 100 W). The desired flexibility to ensure long term sustainability and the imperative energy efficiency gains on the high-throughput tensor computations dominating AI-Native PHYs can be achieved by domain-specialization of many-core programmable baseband processors. Following the domain-specialization strategy, we present TensorPool, a cluster of 256 RISCV32IMAF programmable cores, accelerated by 16 256 MACs/cycle (FP16) tensor engines with low-latency access to 4MiB of L1 scratchpad for maximal data-reuse. Implemented in TSMC’s N7, TensorPool achieves 3643 MACs/cycle (89% tensor unit utilization) on tensor operations for AI-RAN, 6× more than a core-only cluster without tensor acceleration, while simultaneously improving GOPS/W/mm2 efficiency by 9.1×. Further, we show that 3D-stacking the computing blocks of TensorPool to better unfold the tensor engines to L1-memory routing provides 2.32× footprint improvement with no frequency degradation, compared to a 2D implementation.

Index Terms — 6G, AI, RAN, many-core, RISC-V

To read the full article, click here

Related Semiconductor IP

- 250nA-88μA Current Reference - X-FAB XT018-0.18μm BCD-on-SOI CMOS

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

Related Articles

- Physical Design Exploration of a Wire-Friendly Domain-Specific Processor for Angstrom-Era Nodes

- Interstellar: Fully Partitioned and Efficient Security Monitoring Hardware Near a Processor Core for Protecting Systems against Attacks on Privileged Software

- CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

- A Direct Memory Access Controller (DMAC) for Irregular Data Transfers on RISC-V Linux Systems

Latest Articles

- Microarchitectural Co-Optimization for Sustained Throughput of RISC-V Multi-Lane Chaining Vector Processors

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation