Intel, TSMC to detail 2nm processes at IEDM

By Peter Clarke, eeNews Europe (October 8, 2024)

Intel’s attempts to get back to the leading-edge in chipmaking and foundry TSMC’s steps defining that leading-edge will be on show at this year’s International Electron Devices Meeting (IEDM) coming up in December, in San Francisco.

Intel’s attempts to get back to the leading-edge in chipmaking and foundry TSMC’s steps defining that leading-edge will be on show at this year’s International Electron Devices Meeting (IEDM) coming up in December, in San Francisco.

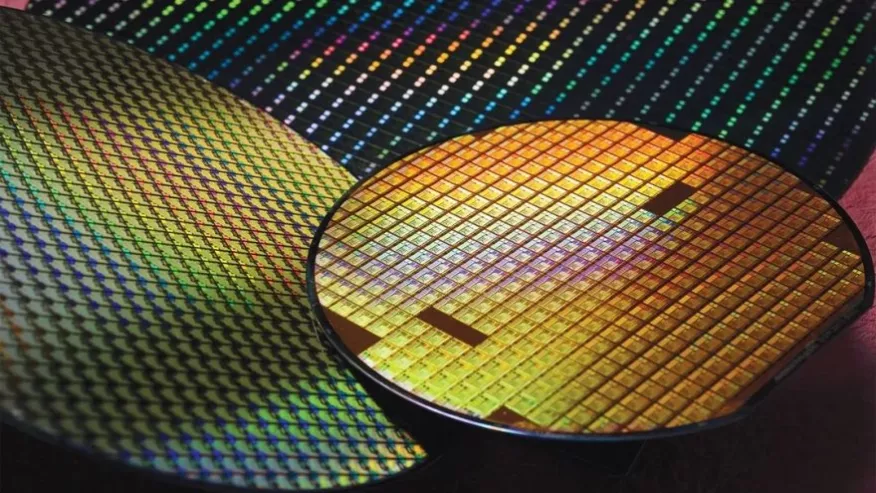

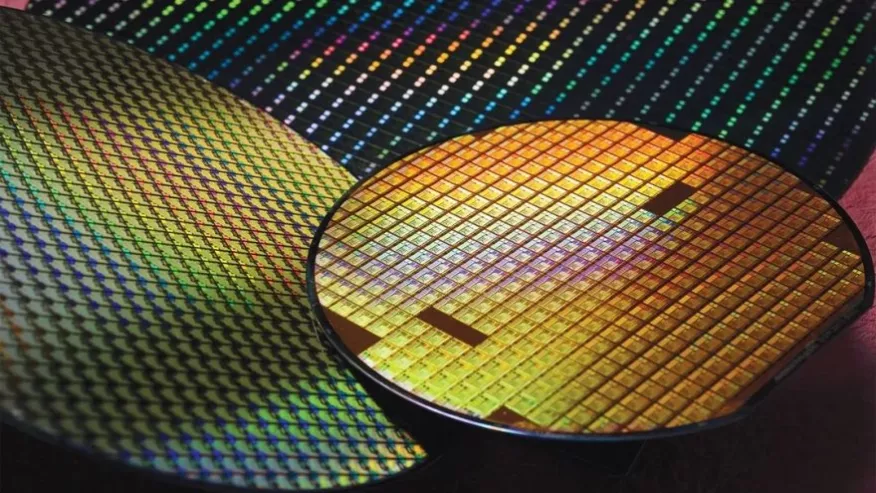

In a late news paper, researchers from TSMC will unveil the N2 manufacturing process, which is a nominal 2nm process designed for computing in AI, mobile and high-performance computing. In the following paper in the same session Intel engineers will provide details of scaling RibbonFETs, the name Intel gives to its nanosheet transistors.

To read the full article, click here

Related Semiconductor IP

- Ultra Ethernet MAC & PCS 100G/200G/400G/800G

- Ethernet PCS 100G/200G/400G/800G/1.6T

- Ethernet MAC 100G/200G/400G/800G/1.6T

- Junction Over-Temperature Detector with Linear Centigrade-to-Voltage Output - X-FAB XT018

- Performance P570 Gen 3

Related News

- Analog Bits to Demonstrate IP Portfolio on TSMC 3nm and 2nm Processes at TSMC 2025 Technology Symposium

- Alphawave Semi Tapes Out Breakthrough 36G UCIe™ IP on TSMC 2nm, Unlocking Foundational AI Platform IP on Nanosheet Processes

- Intel and Cadence Expand Partnership to Enable Best-in-Class SoC Design on Intel's Advanced Processes

- Siemens qualifies industry-leading IC design solutions for Intel Foundry processes

Latest News

- SkyeChip Berhad Delivers 35.0% Net Profit Growth Ahead of Main Market Debut on 20 May 2026

- Quantum eMotion and JMEM TEK Sign Consortium Agreement to Accelerate Quantum-Resilient Semiconductor SoC Development

- Silvaco Announces Immediate Availability of Mixel MIPI C-PHY/D-PHY Combo IP on TSMC N2P Process

- BrainChip Strikes IP Licensing Deal with ASICLAND

- Arteris Technology Adopted by Li Auto for Intelligent Vehicles