IPrium releases BCH Encoder and Decoder

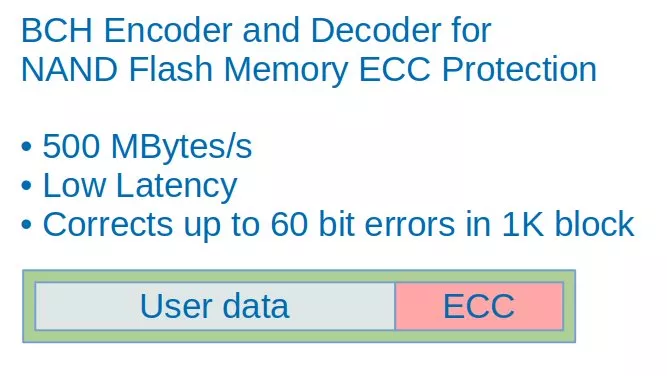

FOGGIA, Italy, November 05, 2024 - FPGA intellectual property (IP) provider IPrium LLC has today announced that it has expanded its family of FEC Encoder and Decoder IP products with a new BCH Codec.

The BCH Codec IP Core supports a wide range of code block and payload sizes up to 8191 bytes with high error correction performance. The IP Core is customizable to any standard, including NAND Flash Memory and DVB.

Pricing and Availability

The BCH Encoder and Decoder IP Core is available immediately in synthesizable Verilog or optimized netlist format, along with synthesis scripts, simulation test bench with expected results, and user manual. For further information, a product evaluation or pricing, please visit the IP Core page:

About IPrium LLC

IPrium Modem IP Cores allow designers of communication equipment to rapidly develop and verify their systems in a highly cost-effective manner. IPrium offers FPGA IP Cores for high-quality wireless and wireline modems. Visit IPrium at www.iprium.com.

Related Semiconductor IP

Related News

- IPrium releases CCSDS TC Telecommand LDPC Encoder and Decoder

- IPrium releases IEEE 802.11n/ac/ax LDPC Encoder and Decoder

- IPrium releases CCSDS TM Telemetry AR4JA LDPC Encoder and Decoder

- IPrium releases 100 Gbps Polar Encoder and Decoder

Latest News

- Arasan Announces immediate availability of its UFS 5.0 Host controller IP

- Bolt Graphics Completes Tape-Out of Test Chip for Its High-Performance Zeus GPU, A Major Milestone in Reducing Computing Costs By 17x

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory

- M31 Collaborates with TSMC to Achieve Tapeout of eUSB2V2 on N2P Process, Advancing Design IP Ecosystem

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs