Cadence Tapes Out UCIe IP Solution at 64G Speeds on TSMC N3P Technology

Delivering the next wave of chiplet innovation, Cadence has successfully taped out its third-generation Universal Chiplet Interconnect Express (UCIe) IP solution, achieving industry-leading 64Gbps per-lane speeds on the advanced TSMC N3P process. As the industry moves toward increasingly complex AI, high-performance computing (HPC), and data center architectures, the need for robust, high-bandwidth chiplet connectivity has never been greater. This milestone positions Cadence at the forefront of enabling scalable, energy-efficient multi-die systems for the most demanding applications.

As process nodes advance to 3nm and below, SoC designers face the challenge of balancing optimal power, performance, and area (PPA) with the requirements of high-speed, reliable die-to-die communication. The Cadence UCIe IP solution, fully compliant with the UCIe specification, is engineered to address these challenges directly. Leveraging TSMC's innovative N3P technology, the solution delivers excellent power efficiency, allowing customers to meet aggressive energy budgets without sacrificing performance.

Tapeout of 64Gbps UCIe IP Subsystem with TSMC N3P

The tapeout of Cadence's UCIe IP at 64G speeds marks a significant leap in chiplet interconnect technology. With support for up to 64Gbps per lane, designers can achieve ultra-high bandwidth density, unlocking new possibilities for scalable chiplet architectures. The solution's flexible and seamless incorporation of the diverse interface protocols available, such as AXI, CXS.B, CHI-C2C, PCIe, and CXL, enables rapid integration into a diverse range of platforms, from AI accelerators and networking appliances to advanced data center systems.

Reliability and integration flexibility are at the core of Cadence's UCIe IP. Advanced error correction, lane margining, and diagnostic capabilities ensure robust operation across heterogeneous multi-die environments. The architecture is designed to simplify system integration, supporting seamless interoperability across multi-vendor chiplet ecosystems.

"Cadence has been at the forefront of die-to-die interface solutions since our first tapeout in 2018. Pivoting to UCIe in 2022, we have extensively demonstrated silicon proofs of our Gen 1 and Gen 2 UCIe solutions over the past two years," said Arif Khan, vice president of marketing in the Silicon Solutions Group at Cadence. "Given the insatiable demand for throughput and efficiency driven by AI and HPC applications, we are proud to make our third-generation UCIe IP—achieving speeds of 64G—available. By collaborating with our trusted partner, TSMC, we are bringing a high-quality and efficient solution to our mutual customers."

Explore UCIe IP:

Industry-Leading Features for AI/HPC Applications

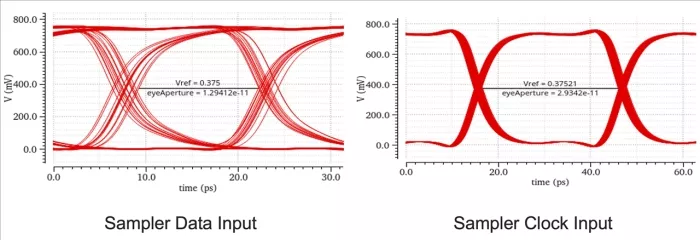

Delivering 64Gbps performance, this solution achieves an impressive bandwidth density of 3.6Tbps/mm in the Standard Package and 21.08Tbps/mm in the Advanced Package. Featuring best-in-class PPA metrics, the architecture is optimized for HPC and AI applications. As with all Cadence UCIe generations, it supports a broad range of protocols—including AXI, CXS, CHI-C2C, PCIe, and CXL.io—seamlessly integrated with the high-speed PHY to provide a complete IP subsystem that accelerates design deployment. Self-calibrating capabilities and hardware-based bring-up eliminate the need for firmware intervention, enabling rapid system initialization and simplifying setup. A streamlined clocking scheme with an integrated phase-locked loop (PLL), combined with robust performance across voltage and temperature variations, ensures reliability and efficiency—allowing designers to focus on what matters most: their core logic.

With this achievement, Cadence expands its comprehensive IP portfolio, providing customers and partners with the tools needed to overcome the challenges of modern computing. By combining higher data rates, expansive and complete customer solutions, and robust standards compliance, Cadence is enabling the next generation of scalable, high-performance systems.

Learn more about Cadence's UCIe IP solution and how it can accelerate your next design at www.cadence.com/designip.

Related Semiconductor IP

- Universal Chiplet Interconnect Express (UCIe™) PHY

- UCIe D2D Adapter & PHY Integrated IP

- UCIe RX Interface

- AXI-S Protocol Layer for UCIe

- UCIe PHY (Die-to-Die) IP

Related News

- GUC Announces Tape-out of UCIe 64G IP on TSMC N3P Technology

- Alphawave Semi Taped-Out Industry Leading 64Gbps UCIe™ IP on TSMC 3nm for the IP Ecosystem, Unleashing Next Generation of AI Chiplet Connectivity

- Cadence Partners with TSMC to Power Next-Generation Innovations Using AI Flows and IP for TSMC Advanced Nodes and 3DFabric

- Alphawave Semi Delivers Cutting-Edge UCIe™ Chiplet IP on TSMC 3DFabric® Platform

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud