Dolphin Integration measures 15% area reduction on 65 nm logic circuit with its 6-Track standard cell library

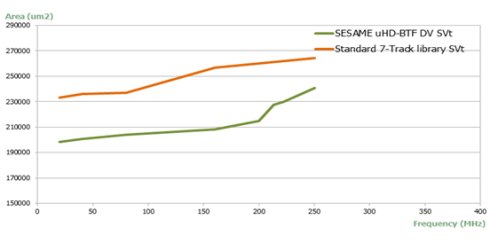

Grenoble, France – September, 21 2012 -- Dolphin Integration today announced the availability of benchmark results on real conditions at TSMC 65 nm LP process, comparing its SESAME uHD-BTF DV standard cell with a 7-Track library:

Highlights:

- SESAME uHD-BTF DV standard cell is 9% to 15% denser after P&R compared to standard 7-Track Library

- Leakage power is reduced 6 times in worst case conditions (SS; 1.08 V; -40°C)

- Low Voltage Capability for additional power savings when operating down to 0.9 V +/-10%

SESAME uHD-BTF DV benefits from replacing classical D flip-flops with pulsed latches acting as “spinner cells”. The main advantage of the spinner cell is a significant improvement in terms of density, 30% compared with D flip-flops!

More information on the key benefits of SESAME uHD-BTF DV standard cell library is available directly on the Presentation sheet

To request an access to the evaluation kit of SESAME uHD-BTF DV standard cell, contact sesame@dolphin-integration.com

About Dolphin Integration

Dolphin Integration is up to their charter as the most adaptive and lasting creator in the Microelectronics Design Industry to "enable mixed signal Systems-on-Chip". It stars a quality management stimulating reactivity for innovation as well as independence and partnerships with Foundries. Their current mission is to supply worldwide customers with fault-free, high-yield and reliable sets of CMOS Virtual Components, such as mixed signal high-resolution converters for audio and measurement applications, Libraries of memories and standard cells, Power management networks, Microcontrollers. The strategy is to follow product launches with evolutions addressing future needs, emphasizing resilience to noise and drastic reductions of power-consumption at SoC level, thanks to their own missing EDA solutions enabling Support Engineering with Application Hardware Modeling as well as early Power and Noise assessment, plus engineering assistance for Risk Control

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

Related News

- Dolphin Integration announce availability of their 6-Track Standard Cell Library SESAME HD for the 65 nm LP process

- Dolphin Integration offers first standard cell library to enable a leakage reduction of 1/350 at 65 and 55 nm

- NASA Selects Ridgetop Group to Develop an Innovative Modular SiGe 130 nm Cell Library

- Dolphin Integration announce the availability of new ROM TITAN and ultra low leakage standard cell library SESAME BIV at TSMC 55 nm LP eFlash

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud