Dolphin Integration announce the availability of new ROM TITAN and ultra low leakage standard cell library SESAME BIV at TSMC 55 nm LP eFlash

Grenoble, France – July 15, 2014 -- Dolphin Integration are proud to announce the availability of the new ROM TITAN and the ultra low leakage SESAME BIV at 55 nm LP eFlash.

These two new products come to enrich the large panoply of Dolphin Integration at 55 nm LP eFlash, which now count: RAM, DpRAM, ROM, foundry sponsored ultra-high-density standard cell library and ultra-low-leakage standard cell library.

The new architecture of ROM, named TITAN allows Dolphin Integration users to:

- reduce their die cost thanks to key patent for high density with a single metal programming layer, earning its qualifier of sROMet

- extend their battery life thanks to a minimal leakage in memory periphery

- facilitate integration with a large number of MUX options and high flexibility for address range

Tha ultra low leakage standard cell library allows for its part to:

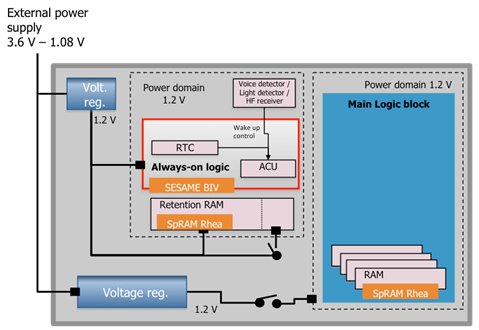

- reduce drastically the leakage (1/700) compared to a traditional standard cell library

- power always-on logic power domains thanks to direct battery connection

- reduce the die cost thanks to the absence of regulators (low BoM)

For more information about the:

- sROMet TITAN TSMC 55 nm LP eF click here

- SESAME BIV TSMC 55 nm LP eF click here

Or contact Dolphin Integration Library Marketing Manager at libraries@dolphin-ip.com

About Dolphin Integration

Dolphin Integration contribute to "enabling mixed signal Systems-on-Chip". Their focus is to supply worldwide customers with fault-free, high-yield and reliable kits of CMOS Virtual Components of Silicon IP, based on innovative libraries of standard cells, flexible registers and low-power memories. They provide high-resolution converters for audio and measurement, regulators for efficient power supply networks, application optimized micro-controllers.

They put emphasis on resilience to noise and drastic reductions of power-consumption at system level, thanks to their own EDA solutions missing on the market for Application Hardware Modeling as well as early Power and Noise assessment In addition strong experiences in ASIC/SoC design and fabrication, plus privileged foundry portal even for small or medium volumes, makes them a genuine one-stop shop covering all customers’ needs for specific requests.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

Related News

- Dolphin Integration offers first standard cell library to enable a leakage reduction of 1/350 at 65 and 55 nm

- Dolphin Integration announce availability of their 6-Track Standard Cell Library SESAME HD for the 65 nm LP process

- NASA Selects Ridgetop Group to Develop an Innovative Modular SiGe 130 nm Cell Library

- Dolphin Integration announces a new generation of ultra-dense standard cell library for GSMC 0.18 mm uLL eFlash process

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud