RapidIO Intel® FPGA IP

Intel is discontinuing the intellectual property (IP) for RapidIO I and RapidIO II Intel offers two distinct Intel® FPGA IPs for …

Overview

Intel is discontinuing the intellectual property (IP) for RapidIO I and RapidIO II

Intel offers two distinct Intel® FPGA IPs for RapidIO:

- RapidIO II Intel® FPGA IP complies with the RapidIO Specification Revision 2.2

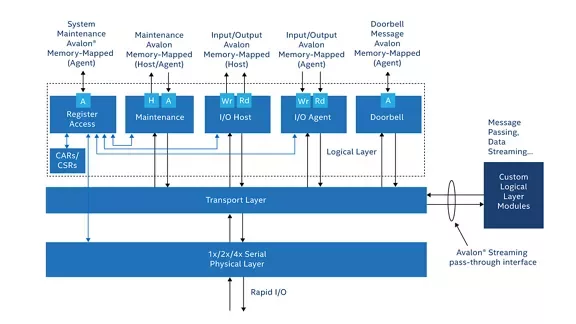

- Physical, transport, and logical layer separations (modular architecture)

- IDLE2 sequence - long control symbol

- 1.25, 2.5, 3.125, 5.0 and 6.25 Gbaud lane rates with 1X, 2X, and 4X link widths

- RapidIO Intel® FPGA IP complies with the RapidIO Specification Revisions 1.3 / 2.1

- Physical, transport, and logical layer separations (modular architecture)

- IDLE1 sequence - short control symbol

- 1.25, 2.5, 3.125, and 5.0 Gbaud lane rates with 1X and 4X link widths

For device support details, such as lane rates, link widths, and speed grades, refer to the RapidIO Intel® FPGA IP user guides.

A significant portion of the wireless industry adopts the RapidIO standard as a high-speed interconnect. The RapidIO standard is typically used between digital signal processors as well as between the control plane processors and memory. RapidIO is also gaining acceptance as a backplane interconnect due to its adoption of widely used standards for the electrical characteristics of the physical media attachment (PMA), such as XAUI or CEI for up to 6.25 Gbaud data rate. Intel® FPGAs are also capable of supporting RapidIO Gen3 data rates.

For a system-level integration-ready solution, you can save several months of design time by selecting all RapidIO layers—including features, such as address translation as well as simple Avalon® Memory-Mapped (Avalon-MM) and Avalon® Streaming (Avalon-ST) FIFO interfaces.

Protocol Solution

One of the images shows an example of a system built using the Platform Designer with a Nios® II soft embedded processor as a processing element. The program memory can include “boot code” for system-level enumeration of the various endpoints. The program also configures the capability address registers of the endpoints and the Intel® FPGA IP function.

Key features

- PHY based on embedded transceivers

- Easy to use

- Intellectual property (IP) parameter editor allows easy manual optimization of parameters, such as interface FIFO depths, address translation windows, output differential voltage, and pre-emphasis

- Easy configuration provides ways to reduce resource utilization to create smaller Intel® FPGA IP function variations depending on application needs

- Platform Designer for system interconnect

- Robust solution

- Endpoint IP core, testbenches with proven interoperability with leading digital signal processor and switch vendors

- Compliant to RapidIO specification, Revision 1.3 / 2.1 and 2.2

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about RapidIO IP core

How to pick a RapidIO switch

Tips for maximizing RapidIO

RapidIO moves up to Fabric

Enter the Inner Sanctum of RapidIO: Part 1

Enter the Inner Sanctum of RapidIO: Part 2

Frequently asked questions about RapidIO IP cores

What is RapidIO Intel® FPGA IP?

RapidIO Intel® FPGA IP is a RapidIO IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this RapidIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this RapidIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.