AAC-LC Stereo Audio Encoder

The AAC-LC Stereo Audio Encoder (CWda84) is an audio IP core for encoding one stereo stream in real-time.

Overview

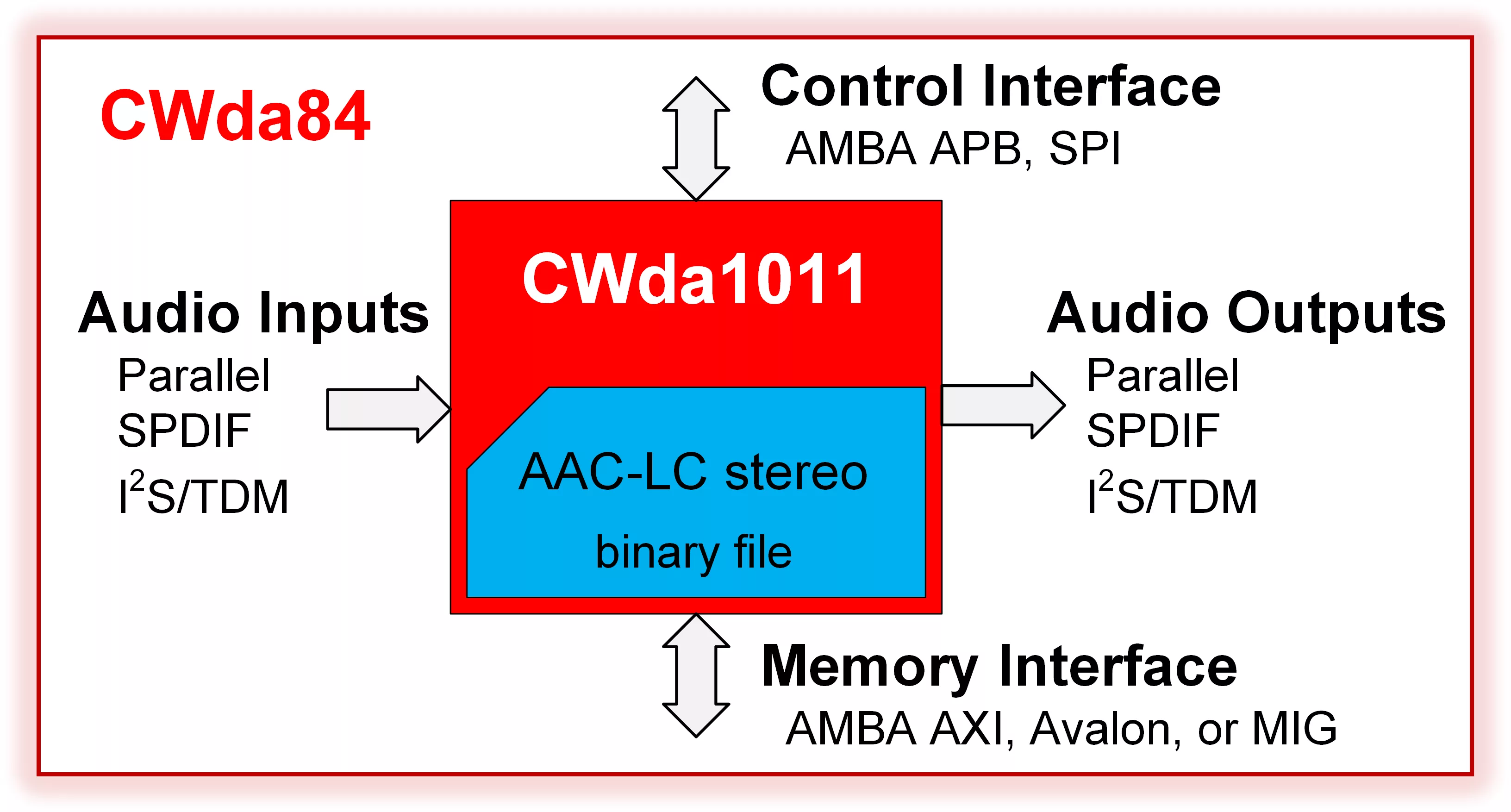

The AAC-LC Stereo Audio Encoder (CWda84) is an audio IP core for encoding one stereo stream in real-time.

This core contains the AAC-LC stereo encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

The software is compiled into an image file (.bin) which can be automatically boot-loaded through one of the control interfaces (parallel AMBA APB or serial SPI) and run on the audio engine platform with simple parameters setting.

The program can be configured, controlled and monitored by means of a configuration, control, and status register file, accessed by the control interfaces.

The audio input and output interfaces uses a native parallel interface. Other standard audio interfaces, such as I2S/TDM and SPDIF are also available.

The interface to the external memory can be one of the following: AMBA AXI (for ASICs or Xilinx FPGAs), Avalon (for Altera FPGAs) or MIG (for Xilinx FPGAs).

The CWda1011 platform is an instance of the generic CWdaXYZ Audio Engine Platform. Other platforms are available for a different number of streams (from one stream, up to 16 streams). Please contact us to select the best solution for your requirements.

Key features

Specifications

- AAC-LC encoders are compliant with the ISO/IEC 13818-7 audio standard, using Fraunhofer IIS high quality software

- Supported channel modes: mono, dual mono, stereo, and joint stereo

- Supported sample rates: 11.025, 12, 16, 22.05, 24, 32, 44.1 and 48 kHz

- Supported transport types: ADTS, LATM, and LOAS

- 16-bit input audio resolution

- Requires 577 kB of external memory

- Configurable output latency useful to synchronize with other sources (e.g. video)

- Minimum latency: 1 frame

- Software interface protocol for control, configuration and monitoring

- Parameter change while muting or repeating one frame

- Real time operation @70 MHz for worst-case settings (maximum bitrate and maximum sampling rate). Results for other settings can be provided upon request

Interfaces

- AMBA-APB and/or SPI for configuration, control and status

- AMBA-AXI, Avalon or Native MIG interfaces for external memory access (instructions and data access)

- I2S/TDM, SPDIF and/or parallel interface for audio input

- Parallel interface for audio output

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Audio Analog IP core

Design and evaluation of power-efficient SoCs

Using audio codecs IP as the digital audio hub in mobile multimedia systems

Consumer IC Advances -> Altering algorithms to create '3D' sound

Efficient audio is essential for low-power 3G mobiles

Application Hardware Modeling: Selective modeling for early prediction of subsystem performances through simulation

Frequently asked questions about Audio Analog IP cores

What is AAC-LC Stereo Audio Encoder?

AAC-LC Stereo Audio Encoder is a Audio Analog IP core from Coreworks, S.A. listed on Semi IP Hub.

How should engineers evaluate this Audio Analog?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Audio Analog IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.