UFS Verification IP

UFS Verification IP is compliant with JESD220E UFS specification and verifies UFS devices.

Overview

UFS Verification IP is compliant with JESD220E UFS specification and verifies UFS devices. UFS Verification IP is developed by experts who have worked on complex protocols before. We have proven Unipro and MPHY Verification IP's and UFS is build on top of it to make it robust.

UFS Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

UFS Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full UFS Host and Device functionality.

- Compliant testsuite as per JESD224 document.

- Supports high performance M-PHY type-1

- Supports full UFS Host and Device functionality.

- Supports UFS driver layer over UniPro

- Supports Verification IP interface at MPHY Serial, MPHY RMMI, Unipro CPort level

- Supports UFS-Specified commands of Specification JESD220E

- Supports Unified Memory Extension JESD220-1A(Version 1.1)

- Supports various UFS layers

- UFS Command Set Layer (UCS)

- UFS Transport Protocol Layer (UTP)

- UFS Interconnect Layer (UIC)

- Includes MIPI UniPro and M-PHY Verification IP for UFS Interconnect Layer verification

- MIPI UniPro is adopted for data link layer

- MIPI M-PHY is adopted for physical layer

- Proven MIPI UniPro BFM

- Proven MIPI M-PHY BFM

- 1 and 2 lane support

- All PWM gears support

- All HS gears support

- All DME commands supported

- Enter hibernate and exit hibernate supported

- Complex LSS feature verification support to cover all cases, Like lane mapping, reverse lane mapping, errors in UPR sequences etc.

- Various types of error injection at Unipro and MPHY layers

- L1.5 and Cport test mode features supported

- Advanced L1.5, L2 and Cport error injection

- All L2 Preemption and error cases supported

- Supports Unipro 1.41, Unipro 1.6, Unipro 1.8 and Unipro 2.0 specifications

- Supports MIPI MPHY 3.0, MIPI MPHY 4.1 and MIPI MPHY 5.0 specifications

- Low power with multiple power operating modes

- Supported below latest Unipro Version 2.0 features

- Supports HS-G5 gear in HS mode

- Supports Linkstartup sequence start either HS Mode(HS G1A or HS G1B) or LS mode(PWM G1)

- Supports L2 buffer extension

- Supports boot mode operation

- Supports device enumeration and discovery

- Supports Multiple partitions (LUNs) with partition Management

- Supports Multiple User Data Partition with Enhanced User Data Area options

- Supports for boot partitions and RPMB partition

- Supports for Reliable write operation

- Supports for Background operations

- Supports for Secure operations, Purge and Erase to enhance data security

- Supports for Write Protection options, including Permanent & Power-On Write Protection

- Supports for Signed access to a Replay Protected Memory Block

- Supports for HW Reset Signals

- Supports Task management operations

- Supports Power management operations

- Supports automatic/user tag generation

- Supports all Initiator ID values

- Supports UFSHCI as per the specification JESD223C

- Error injection and detection in all levels of UFS protocol

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Supports constraints Randomization.

- Callbacks in host and device for various events.

- UFS Verification IP comes with complete test suite to test every feature of UFS specification.

- Functional coverage analysis for complete UFS features.

- Supports Host Performance Booster Version 1.0 as per latest specification JESD220-3

- Supports below latest UFS Version 3.1 features

- UFS-DeepSleep Power Mode

- Performance Throttling Event Notification

- Write Booster

- Supports below latest UFS Version 4.0 features

- Support advance RPMB

- Support Out of Order

- Support Total EHS length as Non-Zero with 32BWords

- Support Multi-circular Queue (MCQ) in UFSHCI

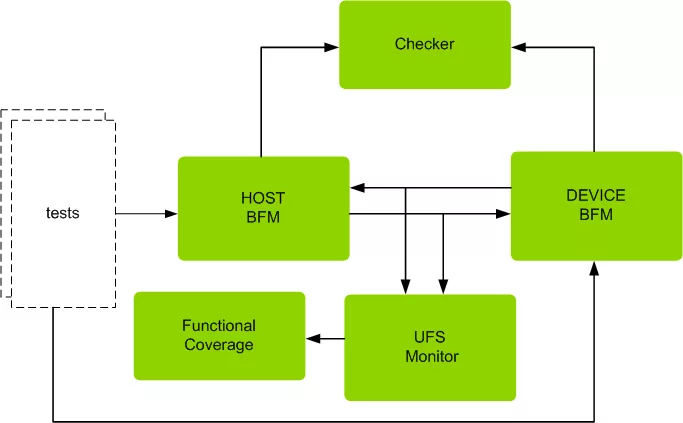

Block Diagram

Benefits

- Rich set of configuration parameters to control the functionality

- Faster testbench development and more complete verification of UFS designs.

- Easy to use command interface simplifies testbench control and configuration of Host,Device and monitor

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the UFS testcases.

- Example's showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UFS Controller IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

UFS or NVMe in Smartphone? See Apple's answer!

UFS Goes Mainstream

eMMC: The Embedded Storage Powering On-Device AI

Frequently asked questions about UFS Controller IP

What is UFS Verification IP?

UFS Verification IP is a UFS Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.