UFS 5.0 Host Controller IP

Universal Flash Storage (UFS) is a JEDEC standard for high performance mobile storage devices suitable for next generation data s…

Overview

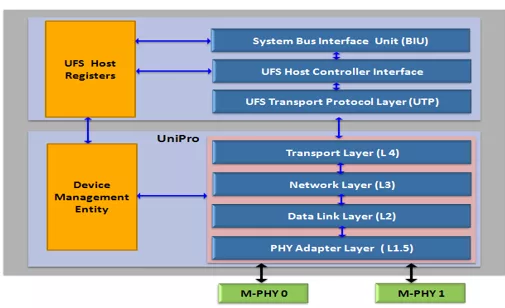

Universal Flash Storage (UFS) is a JEDEC standard for high performance mobile storage devices suitable for next generation data storage. UFS is also adopted by Mobile Industry Processor Interface (MIPI) as a data transfer standard designed for mobile systems. UFS incorporates the MIPI UniPro standard as well as the MIPI Alliance M-PHY standard. Most UFS applications require large storage capacity for data and boot code. Applications include mobile phones, tablets, Digital Still Camera (DSC), Portable Media Player (PMP), MP3, and other applications requiring mass storage, boot storage, XIP or external cards. The UFS standard is a simple but high-performance serial interface that efficiently moves data between a host processor and mass storage devices. UFS transfers follow the SCSI model, but with a subset of Small Computer System Interface (SCSI) commands. The Arasan UFS IP family consists of Host controller IP, Device controller IP, and M-PHY.

The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms. This leads to smaller footprint, greater interoperability between mobile IP, chips and devices from diverse sources, and lower power and Electro Magnetic Interface (EMI).

Arasan’s UFS Host Controller IP, described in this document, is designed for ease of integration, highest interoperability, and fully compliant to the JEDEC standards. It is implemented based on Arasan’s proven MIPI technology, including UniPro and M-PHY.

The UFS 5.0 specification adds HS-GEAR6 as mandatory. The UniPro 3.0 specification adds new attributes and modified some of the existing attributes for each layer.

Key features

Compliant with the following specification versions:

- UFS 5.0 (JESD220H.pdf)

- UFS HCI 5.0 (JESD223G.pdf)

- MIPI UniPro version 3.0(mipi_UniPro_specification_v3-0.pdf)

- MIPI M-PHY version 6.0(mipi_M-PHY_specification_v6-0.pdf)

Interfaces Supported:

- AXI Bus Protocol (AXI)

- Advanced High Performance Bus (AHB)

- High-performance M-PHY type 1

Core Features:

- Two Lanes

- Low power with multiple power operating modes

- Configurable Transmit and Receive First IN First OUT (FIFO)s

- Error Detection and Reporting

- Supports data and task management

- Supports multiple commands and tasks

- Deep Sleep Power mode

- Host Performance Booster (HPB)

- Write Booster

- Out of Order Sequencing of UPIUs

- Support for EHS field

- Queuing mechanism (Circular and Multiple queues)

- Device Level Exception Event

- Host Initiated Defragmentation

- Device Health Exception

- Write Booster Buffer Resizing

- Partial Flush Modes of Write Booster

- Fast Recovery Mode

- Link Equalization Training to identify optimal TX Equalization settings

Block Diagram

What’s Included?

- Synthesizable RMM compliant Verilog RTL code.

- Easy-to-use Verilog test environment.

- Synthesis scripts

- Technical documents

- User guide

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about UFS Controller IP core

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Vertically Integrated MIPI Solutions

Design & Verify Virtual Platform with reusable TLM 2.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

Frequently asked questions about UFS Controller IP

What is UFS 5.0 Host Controller IP?

UFS 5.0 Host Controller IP is a UFS Controller IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.