Verification IP for UFS

Accelerated confidence in simulation-based verification of RTL designs with embedded storage interfaces such as UFS, UniPro, M-PH…

Overview

Accelerated confidence in simulation-based verification of RTL designs with embedded storage interfaces such as UFS, UniPro, M-PHY

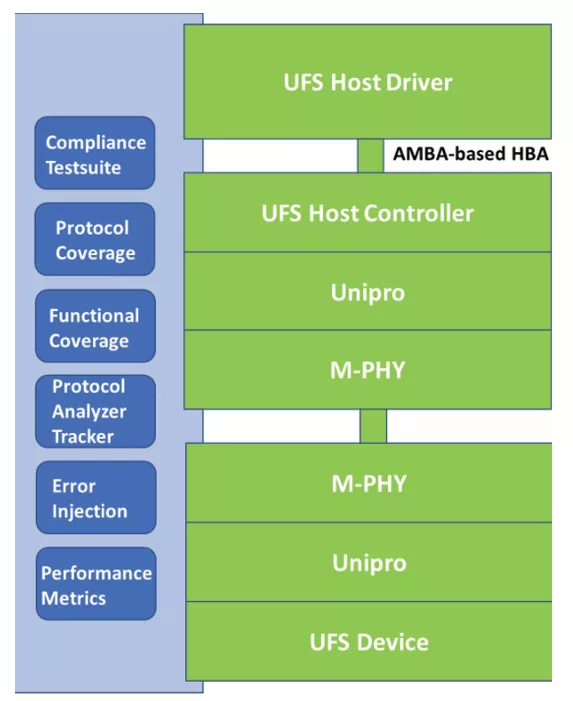

Avery UFS/Unipro VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates: constrained random SCSI and Unipro traffic generation, robust packet and physical layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debugging, and performance analysis metrics.

With the advanced capabilities of Avery VIP, engineers can work more efficiently, develop more complex tests, and work more on verifying both low-level and system-level functions.

Avery compliance test suites offer effective core-through-chip-level tests, includ ing those used in compliance workshops as well as extended tests developed by Avery to cover the specification features.

Key features

UFS VIP is a comprehensive VIP solution portfolio for SoC and IP designs incorporating the UFS Host Controller (UFSHCI), UFS 4.0, and UME standard, in conjunction with the MIPI Unipro and M-PHY standards.

- UFS host supported two ways:

- UFSHC 4.0 driver model supports UME 1.0 and implements UFSHCI programming interface, including host adapter to various host bus interfaces, including AMBA AXI and AHB

- Generic host model emulates UFSHC host driver and UFSHCI-based controller

- UFS device model emulates simple UFS device, including sparse logical block storage and processes over 20 SCSI

- Supports command sets: Native UFS and SCSI SPC-4, SBC-3, and SAM-5

- Supports UFS DME and CPort users

- CPort adapter interfaces to Avery or third party UniPro IP/VIP, enabling mix and match between UFS and Unipro layers to support module-level integration and verification

- M-PHY model

- Support draft M-PHY 5.0 Multiple LANE provisions

- Multiple transmission modes include LS-MODE NRZ and PWM signaling Multiple power saving modes

- Support error injections (encoding, disparity, etc.)

- UniPro model

- Emulates UniPro draft 2.0 protocol stack layers and M-PHY

- Supports all service primitives (SAP) and service data units (x_SDU)

- DME user supports all sequences of control, configuration, and status primitives

- Transport service

- Allocates connections between CPorts

- Schedules message transfers between CPort users

- Supports CPort signal interface

- Supports UniPro test feature

- Inject errors at all layers through callbacks

- Comprehensive assertions track UFS and MIPI compliance coverage

- Functional coverage tracks range of packet traffic, FSMs, and complex operational sequences

- Tracker log monitors all levels and improves debug

- Comprehensive directed and constrained random compliance test suite for UFSHCI and UFS device achieves high protocol coverage

Block Diagram

Benefits

- Provides effective core-through-chip-level tests

- Develops more complex tests

- Enables focusing on verifying low-level and system-level functions

- Isolates compliance issues

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about UFS Controller IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

UFS or NVMe in Smartphone? See Apple's answer!

UFS Goes Mainstream

eMMC: The Embedded Storage Powering On-Device AI

Frequently asked questions about UFS Controller IP

What is Verification IP for UFS?

Verification IP for UFS is a UFS Controller IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.