Simulation VIP for UFS

In production since 2012 on multiple production designs.This Cadence® Verification IP (VIP) supports the JEDEC Universal Flash St…

Overview

In production since 2012 on multiple production designs.</lead>

This Cadence® Verification IP (VIP) supports the JEDEC Universal Flash Storage (UFS) standard. The VIP for UFS is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

The JEDEC UFS standard is an emerging standard for storage devices tailored specifically for mobile applications and computing systems requiring high performance and low power consumption. The UFS standard adopts the well-known SCSI architecture model and command protocols supporting multiple commands with command queuing features and enabling a multi-thread programming paradigm. To achieve the highest performance and most power-efficient data transport, JEDEC UFS aligns with industry-leading specifications from the MIPI® Alliance to form its Interconnect Layer.

Supported Specifications: Latest proposals balloted at JEDEC for UFS 4.0 and the official specifications for UFS 1.1, UFS 2.0, UFS 2.1, UFS 3.0 and UFS 3.1.

Key features

- Interfaces

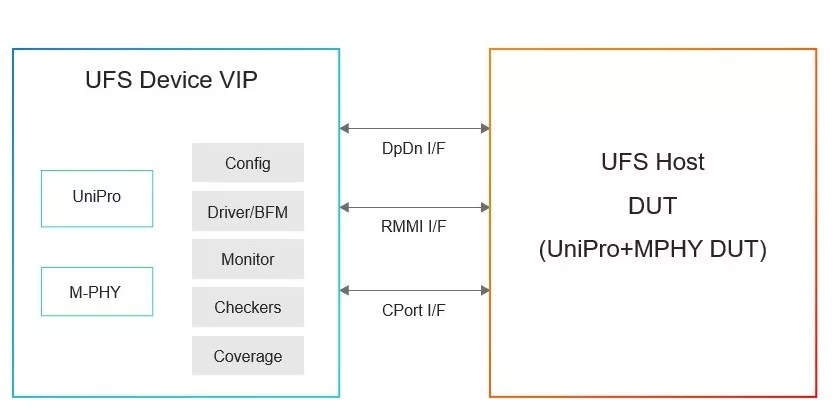

- DPDN I/F and RMMI I/F when used with UniPro VIP. CPort signaling pin I/F and CPort message using transactions

- UTP Layer - UPIUs

- NOP IN, NOP OUT, Query Request/ Response, Task Management Request/ Response, Command, Response, Data Out, Data In

- UCS Layer - SCSI Commands

- READ (6, 10, 16), WRITE (6, 10, 16), Inquiry, Report LUNs, Read Capacity (10, 16), Test Unit Ready, Verify, Start Stop Unit, Mode Sense, Request Sense, Security Protocol In, Security Protocol Out, Send Diagnostic, Read Buffer, Write Buffer, Pre-Fetch (10, 16), Synchronize Cache (10, 16), Mode select, Unmap, and Format

- UFS Protocol Features

- Boot functionality

- LUNS and W-LUNS supported

- Interleaving of commands supported

- Types of queue supported : Shared queue and Per-LUN queue

- CPort Signaling Interface

- As specified by UniPro Specification:

- CPort connection to Device UniPro

- Direct CPort connection to Host UniPro

- Supported Use Cases

- UFS standalone (Transaction mode or using CPort signaling interface)

- Full-stack UFS (with UniPro+M-PHY over DPDN serial interface or with UniPro only over RMMI interface)

- UFS 3.0 Support

- Support for HS Gear 3 and 4, IID feature in Task Management request UPIUs, Device Health Descriptor

- UFS 3.1 Support

- HPB, WriteBooster Buffer, Deep Sleep Power Mode, Performance Throttling

- UFS 4.0 Support

- EHS and its usage in RPMB, OOO RTT and DataIn transmission, HPB 2.0, ARPMB

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about UFS Controller IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

UFS or NVMe in Smartphone? See Apple's answer!

UFS Goes Mainstream

eMMC: The Embedded Storage Powering On-Device AI

Frequently asked questions about UFS Controller IP

What is Simulation VIP for UFS?

Simulation VIP for UFS is a UFS Controller IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.