UCIe D2D Adapter

Industry , Silicon Proven, 32 Gbps per pin, backed by a portfolio of verification tools, PHY interoperability and integration.

Overview

Industry Leading, Silicon Proven, 32 Gbps per pin, backed by a complete portfolio of verification tools, PHY interoperability and integration.

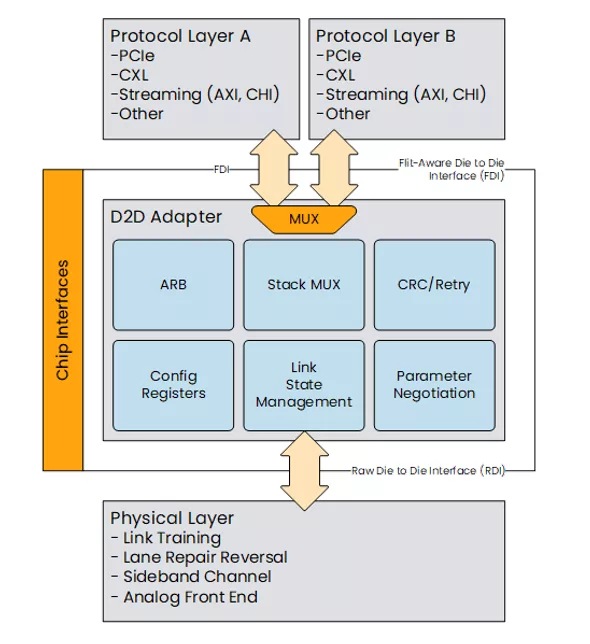

The D2D Adapter for UCIe is a scalable adapter layer between one or more protocol components and the UCIe PHY, which ensures efficient data transfer across the UCIe Link by seamlessly coordinating with the Protocol Layer and Physical Layer. By minimizing logic on the main data path, it delivers a low-latency, optimized pathway for protocol Flits. When handling CXL protocol, the D2D Adapter incorporates ARB/MUX functionality to support multiple simultaneous protocols. For scenarios where the Raw BER exceeds 1e-27, it implements the CRC and Retry scheme defined in the UCIe Specification, ensuring reliable data transport for PCIe, CXL, or other protocols including Streaming protocols.

Additionally, the D2D Adapter manages critical functions such as higher-level Link state machine coordination, parameter exchanges with remote Link partners for protocol options, and power management synchronization when supported. The IP Core is silicon and PHY agnostic implementation of UCIe D2D Adapter following the v2.0 standard, targeting ASIC applications. The IP core is thoroughly tested in System Verilog random regression environment.

The IP comes with the widest parameter set available and has gone through extensive testing. The IP core is silicon proven, heavily tested in UVM regression environment and has been interoperability tested and integrated with a leading UCIe PHY provider.

The Die to Die Adapter IP interfaces to the UCIe Serdes with the Raw Die to Die Interface (RDI) and to the Protocol Layer with the Flit-Aware Die to Die Interface (FDI). The IP is highly customizable and contains blocks for CRC / Retry logic as well as Protocol and Stack Multiplexers

Key features

- Ultra Low Latency

- CRC and Retry, or Parity Computation

- Multiple Protocols,

- Multiple Stacks

- Protocol/Stack Arbitration and Multiplexing

- Link State Management

- Protocol and Parameter negotiation

- Silicon Agnostic

Block Diagram

Benefits

- Test Environment: UCIe D2D Adapter IP is Tested against a VIP model in UVM regression for full functional coverage

- Silicon Agnostic: Designed in Verilog and targeting both ASICs and FPGAs

- PHY Integration: PHY Integration support with additional hours or off the shelf PHY integration package for quick and efficient deployment

- Active Support: All support is actively provided by engineers directly

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report , Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UCIe IP core

Synopsys Advances Die‑to‑Die Connectivity with 64G UCIe IP Tape‑Out

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is UCIe D2D Adapter?

UCIe D2D Adapter is a UCIe IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.