Universal Chiplet Interconnect Express(UCIe) VIP

The UCIe VIP , a solution that offers a comprehensive set of features and capabilities to ensure the quality and performance of y…

Overview

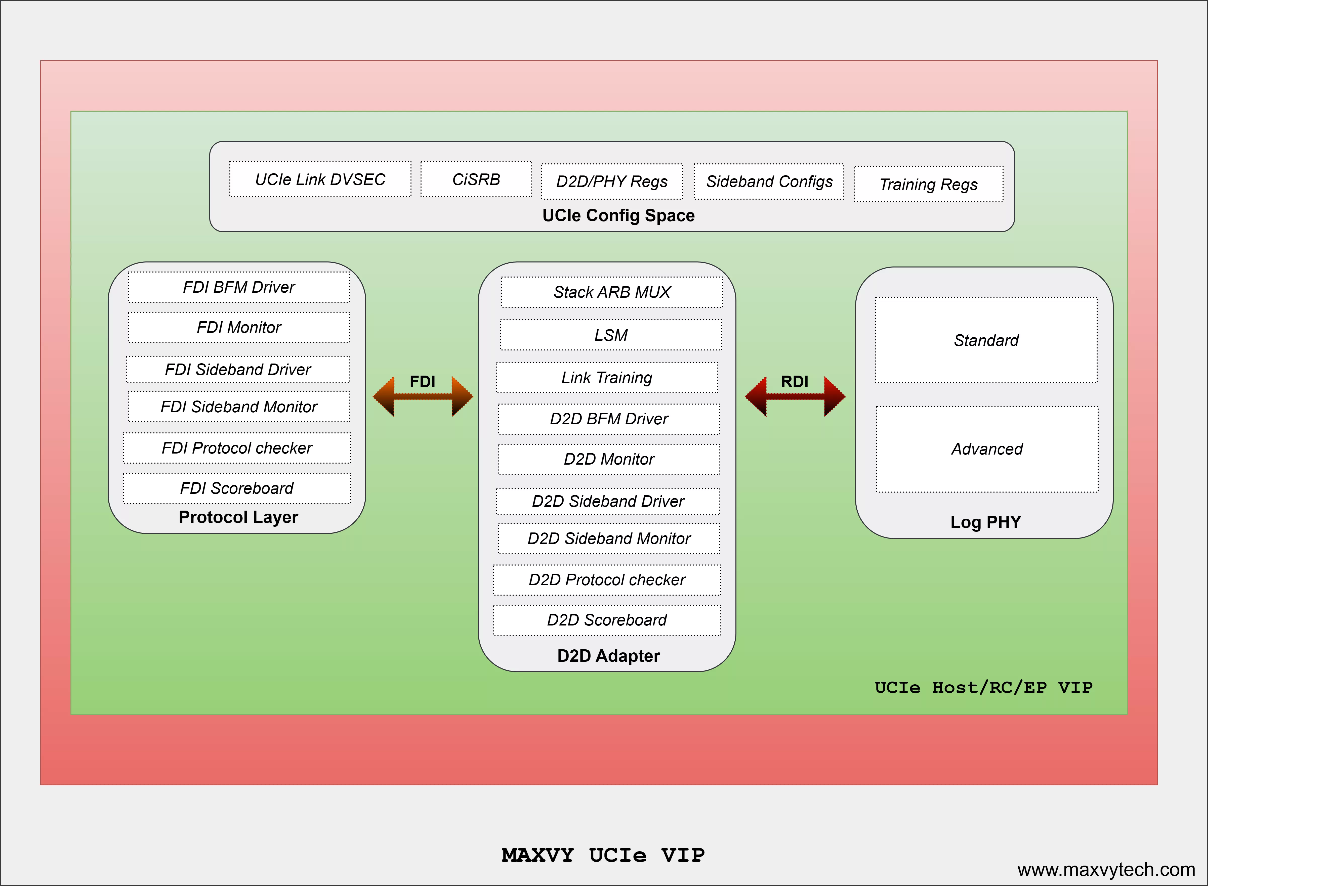

The UCIe VIP , a state-of-the-art solution that offers a comprehensive set of features and capabilities to ensure the quality and performance of your UCIe designs. The UCIe VIP is fully compliant with UCIe Specification version 1.0 and supports all the layers of the UCIe stack, such as FDI, RDI, LogPHY, PCIe, and CXL protocols. The UCIe VIP is also very user-friendly and flexible, with simple APIs, easy integrations, and configurable parameters. You can easily customize and control the UCIe functionality according to your needs. The UCIe VIP also provides a rich set of verification capabilities, such as protocol checks, functional coverage, traffic generation, error injection, and debug tools. You can easily monitor, detect, and report any issues or violations in your UCIe designs. The UCIe VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and supports all leading simulators. With The UCIe VIP, very flexible for unit level testing, you can achieve faster verification closure and higher quality of your UCIe designs.

Key features

- The vendor provides a wide range of features and customer support for its Verification IP (VIP) for UCIe, making it the best choice for verifying your UCIe-based chiplet systems. Here are some of the features and customer support that MAXVY offers:

- Supports Universal Chiplet Interconnect Express Specification Version 1.0, February 2022.

- Support for single and multiple stacks, single and multiple modules, and single and multi-lane configurations.

- Support for different flit modes, such as raw flit, CXL68B enhanced flit, standard and latency-optimized 256B flit.

- Support for ARB/MUX, CRC retry, link state management, parameter negotiation, power management link states, link training, scrambling/descrambling, sideband training transfers, lane repair, lane reversal, mainband/sideband interfaces, FDI/RDI interfaces, etc.

- Support for native SystemVerilog (UVM) and Verilog languages, as well as all major simulators such as cadence xcelium, synopsys VCS, siemens Questasim, xilinx vivado, Aldec Riviera.

- Support for directed and randomized flit generation, error injection at multiple levels, protocol checkers, layered protocol debugging trace files, throughput measurement, compliance test suite, etc.

- Support for UCIe PCIe extended config space, unit-level FDI/RDI driver mode BFMs for standalone PHY testing, RDI BFM for simplified direct protocol/D2D only testing, etc.

- Support for functional coverage for complete UCIe features, monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Support for runtime configurable BFM settings.

Block Diagram

What’s Included?

- Basic Test Suite.

- Encrypted The UCIe VIP package.

- VIP integration guide, user guide.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UCIe IP core

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is Universal Chiplet Interconnect Express(UCIe) VIP?

Universal Chiplet Interconnect Express(UCIe) VIP is a UCIe IP core from MAXVY Technologies Pvt Ltd listed on Semi IP Hub.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.