ITU-R BT.656 Decoder

The DB1840 CCIR 656 Decoder IP Core decodes an ITU-R BT.656 digital video uncompressed NTSC 720x486 (525/60 Video System) and PAL…

Overview

The DB1840 CCIR 656 Decoder IP Core decodes an ITU-R BT.656 digital video uncompressed NTSC 720x486 (525/60 Video System) and PAL 720x576 (625/50 Video System) Standard Definition frame, extracting Y’CbCr 4:2:2 video components, optional Ancillary Data, and frame timing & status signals.

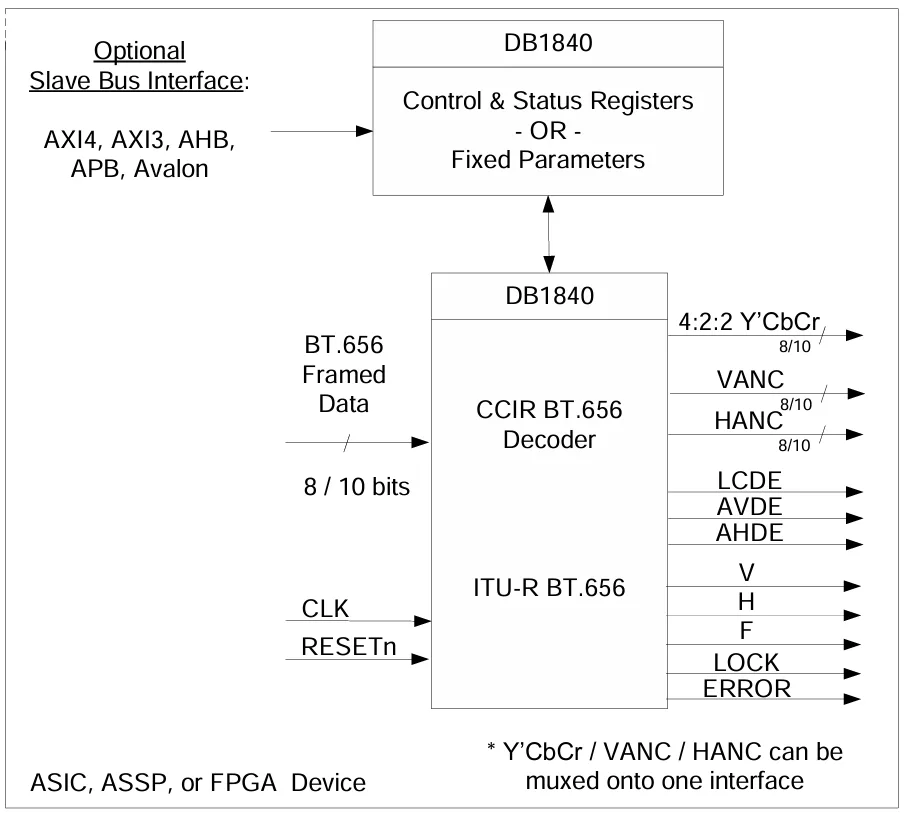

Figure 1 depicts the DB1840 CCIR 656 Decoder IP Core embedded within an integrated circuit device. Control & Status can be programmed into optional DB1840 registers via a bus interface, or set as non-register fixed parameters at synthesis.

Key features

- Decodes an CCIR ITU-R BT.601 Frame providing the following outputs:

- Y’CbCr color digital components (Luma/Chroma)

- Data Enable for Luma / Chroma component samples

- V, H, F timing synchronization

- Status - Lock & Error detection

- Decodes optionally the following:

- Vertical / Horizontal Ancillary Data

- Data Enables for Vertical / Horizontal Ancillary Data

- Optional 8/10-bit Data extraction

- Supports following Standard Definition:

- NTSC 720x486 (525/60 Video System)

- PAL 720x576 (625/50 Video System)

- 27 MHz Sampling Rate

- User optional Slave Bus Interface for programming Control & Status Registers

- Optional Features:

- FIFO – for buffering & separate clock domain interface

- Chroma Re-sample to 4:4:4 Y’CbCr

- Color Space Conversion from Y’CbCr to RGB

- Member of Digital Blocks’ Video Signal & Image Processing IP Core Family, which include the following:

- DB1800 - Standard Definition NTSC/PAL/SECAM Video Sync Separator

- DB1810 - Color Space Convert

- DB1820 - Chroma Resampler

- DB1825 - RGB to YCrCb Color Space Convert with 4:4:4 to 4:2:2 Chroma Resampler

- DB1830 – CCIR BT.656 Encoder

- DB1840 – CCIR BT.656 Decoder

- DB1892 - RGB to CCIR601/656 Encoder

- On-Chip Interconnect Compliance (optional) – Avalon/Qsys, AXI, AXI4, AHB:

- AMBA AXI4 Protocol Specification (V3.0)

- AMBA AXI3 Protocol Specification (V1.0)

- AMBA AHB Specification 2.0

- AMBA APB Specification 2.0

- Avalon Interface Specification (MNL-AVABUSREF-2.0)

- FPGA Integration Support:

- Altera Quartus II & Qsys / SOPC Integration & NIOS II EDS Reference Design

- Xilinx ISE Design Suite utilizing AMBA AXI4 & Embedded Development & Software Development Kits

- ASIC / ASSP Design-In Support:

- Compliance to RTL Design & Coding Standards

- Digital Blocks Support Services

- Fully-synchronous, synthesizable Verilog RTL IP Core, with rising-edge clocking, No gated clocks, and No internal tri-states

Block Diagram

What’s Included?

- The DB1840 is available in FPGA netlist or synthesizable RTL Verilog, along with Synopsys Design Constrains, a simulation test bench with expected results, reference design, and user manual.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is ITU-R BT.656 Decoder?

ITU-R BT.656 Decoder is a Video Transport IP core from Digital Blocks, Inc. listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.