SLC NAND Memory Model

SLC NAND Memory Model provides an smart way to verify the SLC NAND component of a SOC or a ASIC.

Overview

SLC NAND Memory Model provides an smart way to verify the SLC NAND component of a SOC or a ASIC. The SmartDV's SLC NAND memory model is fully compliant with standard SLC NAND Specification and provides the following features. Better than Denali Memory Models.

SLC NAND Memory Model is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SLC NAND Memory Model comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports SLC NAND memory devices from all leading vendors.

- Supports 100% of SLC NAND protocol standard.

- Supports all the SLC NAND commands as per the specs.

- Provides cost effective solutions for mass storage applications.

- Supports the following devices

- 8

- 16

- Supports multiplexed Address/Data.

- Supports page size of (512 + 16 spare) Bytes for x8 device.

- Supports page size of (256 + 8 spare) words for x16 device.

- Supports Block size of (16k + 512 spare) Bytes for x8 device.

- Supports Block size of (8k + 256 spare) words for x16 device.

- Supports page read/program.

- Supports Copy back program mode for fast page copy without external buffering.

- Supports Fast block erase time of 2ms.

- Supports status register.

- Supports Electronic signature.

- Supports Chip enable don’t care.

- Supports Hardware data protection.

- Supports Data integrity of 100,000 program/erase cycles.

- Notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- Implemented in Unencrypted OpenVera, Verilog, System C and System Verilog.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Constantly monitors SLC NAND behavior during simulation.

- Protocol checker fully compliant with SLC NAND Specification.

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- Built in functional coverage analysis.

- Supports Callbacks, so that user can access the data observed by monitor.

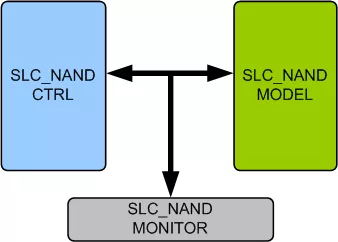

Block Diagram

Benefits

- Faster testbench development and more complete verification of SLC NAND designs.

- Easy to use command interface simplifies monitor control and configuration.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SLC NAND testcases.

- Examples showing how to connect and usage of Model.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about NAND Flash IP core

Concealable physical unclonable functions using vertical NAND flash memory

NAND Flash Memory - Key Element For Your Multi-Die Systems Verification - Part 1

A Tour of the Basics of Embedded NAND Flash Options

Scaling NAND flash to 20-nm node and beyond

Cadence support for the Open NAND Flash Interface (ONFI) 3.0 controller and PHY IP solution + PCIe Controller IP opening the door for NVM Express support

Frequently asked questions about NAND Flash IP

What is SLC NAND Memory Model?

SLC NAND Memory Model is a NAND Flash IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this NAND Flash?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this NAND Flash IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.