ONFI 5.0 Verification IP

The ONFI Verification IP provides an effective & efficient way to verify the ONFI components of an IP or SoC.

Overview

The ONFI Verification IP provides an effective & efficient way to verify the ONFI components of an IP or SoC. The VIP is fully compliant with ONFI-5.0 specifications. The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

Key features

- Compliant to ONFI-2.3 ,ONFI-3.0 ,ONFI-4.0 ,ONFI-4.1 , ONFI-4.2 and ONFI-5.0 specifications.

- Supports all mandatory and optional commands. Supports generation of Vendor Specific Commands.

- Supports up to 16-bit bus width operations.

- Supports implicit and explicit training (DCC, Read DQ, Write DQ Tx, Write DQ Rx).

- Supports SDR, DDR, NV-DDR2, and NV-DDR3 data interface with all timing modes.

- Supports ECC mechanism using BCH encoding.

- Backdoor access from the device to check data integrity.

- On-the-fly protocol and data checking.

- Supports run-time selection of part-number for configuration of parameter page in the NAND Flash Device.

- Supports Callbacks for accessibility of the data observed by components.

- ONFI Verification IP comes with a complete test suite to test every feature of ONFI specification.

- Support for selecting vendor part number/ user-defined part number during runtime.

- Supports Multi package integration and CE_n reduction.

- Supports configurable timing parameters.

- Provides an Error masking mechanism.

- Integrates easily in any verification environment.

- Supports full-timing models or bus functional models.

- Supports a wide variety of Error Injection scenarios.

- Built-in functional coverage analysis.

- Debug log support for each component.

- Provides GUI model for easy debugging.

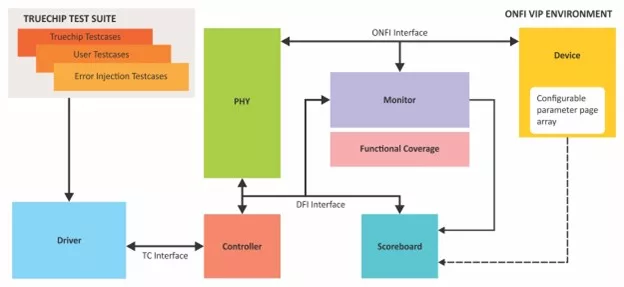

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

What’s Included?

- ONFI controller BFM/Agent

- ONFI devise BFM/ Agent

- ONFI Monitor & Scoreboard

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests and Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about NAND Flash IP core

Concealable physical unclonable functions using vertical NAND flash memory

NAND Flash Memory - Key Element For Your Multi-Die Systems Verification - Part 1

A Tour of the Basics of Embedded NAND Flash Options

Scaling NAND flash to 20-nm node and beyond

Cadence support for the Open NAND Flash Interface (ONFI) 3.0 controller and PHY IP solution + PCIe Controller IP opening the door for NVM Express support

Frequently asked questions about NAND Flash IP

What is ONFI 5.0 Verification IP?

ONFI 5.0 Verification IP is a NAND Flash IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this NAND Flash?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this NAND Flash IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.