ONFI 2 NAND Flash Controller IP Compliant to JEDEC

The ONFI 2.3 NAND Flash Controller IP Core is a full-featured, easy to use, synthesizable core, easily integrated into any SoC or…

Overview

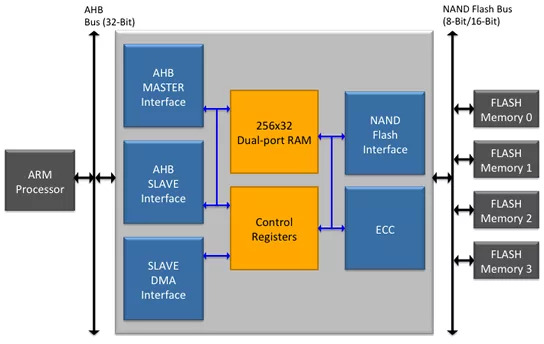

The ONFI 2.3 NAND Flash Controller IP Core is a full-featured, easy to use, synthesizable core, easily integrated into any SoC or FPGA development. Designed to support both SLC and MLC flash memories, ONFI 2.3 NAND controller IP is flexible in use and easy in implementation. The controller works with any suitable NAND Flash memory device up to 128 Gb from leading memory providers – Micron, Samsung, Toshiba and Hynix. The IP core includes a host of configuration options from page size to band selects. The controller offers Hamming Code (1-Bit error correction and 2-Bit error detection) and BCH (option for 4-, 8-, 12-, up to 32-Bit error correction) error code correction (ECC) for optimized performance and reliability. Additional features include the capability to boot from flash.

ONFI2.3 NAND Controller IP core supports the Open NAND Flash Interface Working Group (ONFI) 1.0, 2.0, 2.1, 2.2 and 2.3 standards and the Micron ClearNAND. It can also support a variety of host bus interfaces for easy adoption into any design architecture – AHB, APB, OCP, 8051 or custom buses. The slave AHB IP supports an external DMA interface where the master AHB incorporates an internal DMA controller.

An optional NAND Flash File system is available to support advanced features. The file system converts complicated tasks of NAND flash memory interfacing to simple memory access. Flash memory read, write, garbage collection, bad block management and other functions are handled in the background by the file system.

Key features

- Compliant to ONFI 2.3

- Supports speed ranging from 40MB/s to 200MB/s

- Supports synchronous modes

- Supports asynchronous mode [0-5]

- Supports Flash devices up to 128Gb

- Boot mode support

- Supports all mandatory commands and selected optional commands

- Full access to spare area

- Supports Interleaving Operations

- Page Program Interleaving

- Copy back Program Interleaving

- Block Erase Interleaving

- Read Interleaving

- Cache Interleaving

- Supports Multi LUN/DIE Operations

- Supports Small Data Move

- Supports Change Row Address

- Supports Reset LUN

- Supports EZ – NAND devices

- Supports Micron ClearNAND

- Supports CE# pin reduction mechanism

- Supports volume addressing and volume select command

- Supports a Interrupt(INTR#) signal which provides hardware method of indicating when a command is complete

- Supports commands like Volume select(E1h), LUN status(71h), Device status(72h), Get next operation status(77h), Operation status (7Dh)

- Supports Queue page read and Program page pause

Configuration

- Page Size – 512B, 2KB, 4KB, 8KB, 16KB

- Bank/chip select options

- Programmable timing

- Address cycles – 4, 5

- ECC – enable, disable

- Flash data bus width

Block Diagram

Benefits

- Fully compliant core

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglass

What’s Included?

- RMM Compliant Synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about NAND Flash IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Universal Flash Storage: Mobilize Your Data

Arasan’s xSPI/eMMC5.1 PHY: Unified Dual-Mode Physical Layer IP

UFS Goes Mainstream

ONFI 5.2: What’s new in Open NAND Flash Interface's latest 5.2 standard

Frequently asked questions about NAND Flash IP

What is ONFI 2 NAND Flash Controller IP Compliant to JEDEC?

ONFI 2 NAND Flash Controller IP Compliant to JEDEC is a NAND Flash IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this NAND Flash?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this NAND Flash IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.