ONFI 5.0 NAND Flash Controller IP Compliant to JEDEC

The NAND flash controller IP provides easy, reliable access to an off-chip NAND flash.

Overview

The NAND flash controller IP provides easy, reliable access to an off-chip NAND flash. It supports all modes of the Open NAND Flash Interface (ONFI) Specification, revision 5.0, release candidate 0.5, dated 1 March 2021. It is backwards compatible, supporting the Single Data Rate (asynchronous) mode, the double data rate moves NV-DDR, NV-DDR2, and NVDDR3, to include the latest NV-LPDDR4 recently introduced in the latest revision. All posted rates for these various modes are also supported, from the NV-DDR 33MHz mode at the low end all the way up to the newer 1,200MHz (2.4GT/s) I/O speeds.

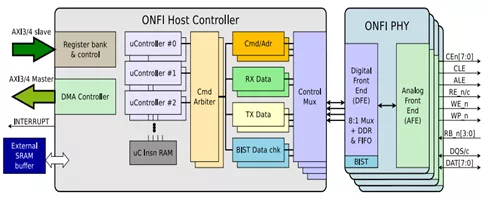

The IP consists of two primary components: a host controller and two or more high speed PHY interface controllers. The host controller is controlled via an AXI slave port. A scatter/gather DMA provides a separate AXI master port, allowing for extended unattended reads or writes. The host controller supports either AXI3 or AXI4, and a user configurable data path width.

Key features

- ONFI v5.0 compliant + Up to 2.4GByte/s.

- All I/O modes implemented + SDR + NV-DDR + NV-DDR2/3 + NV-LPDDR4

- Wide hardware support + Four 8-bit data paths + 8 NAND targets each + Data bus inversion.

- Full PLL support + PLL within PHY + 10MHz SDR + 1.2GHz NV-LPDDR4 + Everything in between

- Configurable AXI ports — AXI3 or AXI4 — 32b–1024b bus widths

- AXI DMA master — Scatter / Gather — Parameterized width — Max Bus Throughput

- PHY BIST support

- Multiple host target processors — Maximizes throughput

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about NAND Flash IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Universal Flash Storage: Mobilize Your Data

Arasan’s xSPI/eMMC5.1 PHY: Unified Dual-Mode Physical Layer IP

UFS Goes Mainstream

ONFI 5.2: What’s new in Open NAND Flash Interface's latest 5.2 standard

Frequently asked questions about NAND Flash IP

What is ONFI 5.0 NAND Flash Controller IP Compliant to JEDEC?

ONFI 5.0 NAND Flash Controller IP Compliant to JEDEC is a NAND Flash IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this NAND Flash?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this NAND Flash IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.