Simulation VIP for SMBus

Incorporating the latest protocol updates, the Cadence® Verification IP (VIP) for SMBus provides a bus functional model (BFM), in…

Overview

Incorporating the latest protocol updates, the Cadence® Verification IP (VIP) for SMBus provides a complete bus functional model (BFM), integrated automatic protocol checks and coverage model. The VIP for SMBus is designed for easy integration in testbenches at IP, systems-on-chip (SoC), and system levels, and helps to reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for SMBus runs on all major simulators and supports SystemVerilog verification language along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specification: SMBus v3.0

Key features

- SMBus Devices

- Controller target, or host

- Packet Error Checking

- Performs PEC on transmit and receive data on applicable packets

- Address Resolution Protocol

- Resolve addresses for devices on the bus

- Device Timeout

- Device timeout condition detection

- Bus Protocol

- All bus protocols with and without a packet error code

- Alert Response Address

- Alert response protocol for device controller capability

- Clock Generation and Data Arbitration

- Clock generation using defined clock timings and data arbitration

- Clock Synchronization Between Two Controllers

- Clock synchronization when more than one controller drives clock

- Optional SMBus Signals

- SMBSUS in suspend-resume mode signal and SMBALERT for (interrupt line for target signal)

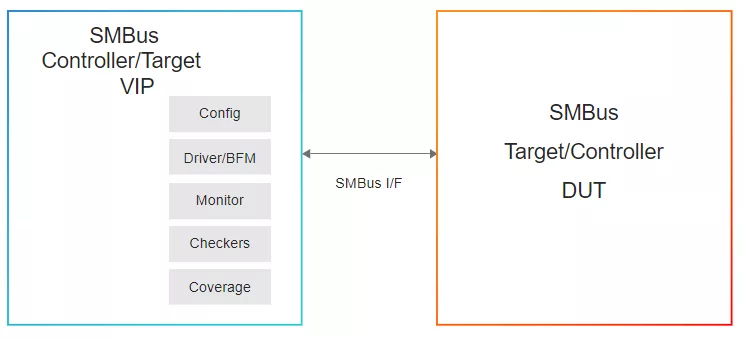

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is Simulation VIP for SMBus?

Simulation VIP for SMBus is a I2C / I3C IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.