Simulation VIP for LPDDR6

The Gold Standard Memory Model is intended to be compatible with the anticipated JEDEC LPDDR6 standard for your IP, Subsystem, So…

Overview

The Gold Standard Memory Model is intended to be compatible with the highly anticipated JEDEC LPDDR6 standard for your IP, Subsystem, SoC, and System-level Design Verification in High-performance Computing and Artificial Intelligence.

First-to-market, with Multiple Early Adopters of Production Designs, targeting full LPDDR6 support. In Production Since 2023.

This Verification IP (VIP) is intended for modeling the upcoming JEDEC Low-Power Memory Device, LPDDR6 design specification. It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for LPDDR6 is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

LPDDR6 is the highly anticipated next generation of the popular LPDDR memory standard, planned by JEDEC to increase memory speed and efficiency, targeting the mobile devices artificial intelligence application space. The LPDDR6 standard is an industry-leading low-power volatile (DRAM) device memory standard for the storage of system code, software applications, and user data. The LPDDR6 Low-Power Memory Device Standard is designed to satisfy the performance and memory density demands of the latest generation of mobile devices such as smartphones, tablets, ultra-thin notebooks, and similar connected devices on the newest, high-speed 4G/5G networks.

Supported specifications: The VIP for LPDDR6 Memory Model supports the latest proposals, which are balloted at JEDEC for LPDDR6: JESD209-6 dated July 2025.

Key Features

Key features of the LPDDR6 device standard supported by the Cadence VIP for LPDDR6 are listed below:

|

Feature Name |

Description |

|---|---|

|

Speed |

|

|

Device Density |

|

|

General DDR Functionality |

|

|

Training Modes |

|

|

Write Clock |

|

|

Burst Length |

|

|

Data Packet Format |

|

|

RDQS Preamble and Postamble |

|

|

Efficiency Mode |

|

|

Refresh |

|

|

ECC |

|

|

PRAC |

|

|

System Meta Mode |

|

|

Command Clock Sync |

|

|

CA Parity |

|

|

FMR and Alert |

|

|

Inter-rank timing |

|

|

Frequency Set Points |

|

|

Exploration Mode |

|

|

MPC |

|

|

Latency and Frequency Table |

|

|

ODT |

|

|

Duty Cycle Adjuster |

|

| CS Training |

|

| Command Bus Training |

|

| WCK2DQ interval oscillator training |

|

| x6 mode |

|

| Mode Registers |

|

|

Functional Coverage |

Provides a rich functional coverage of the below.

|

|

General Capabilities |

|

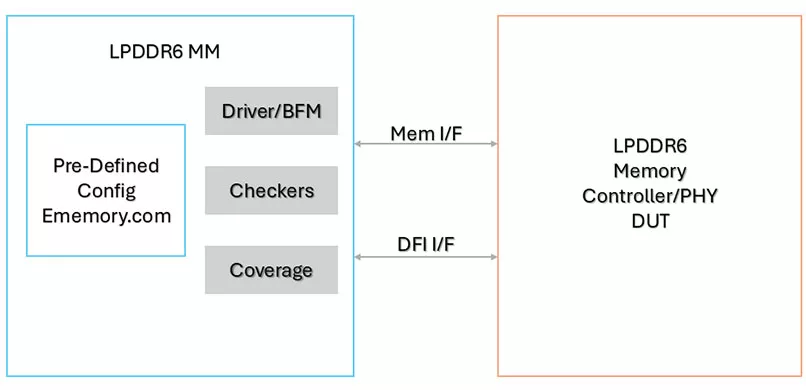

Block Diagram

Benefits

- Hundreds of protocol and timing checkers to easily catch design bugs

- Predefined configurations based on specific speed and density for generic JEDEC definitions available on ememory.com(opens in a new tab)

- Transaction and memory callbacks for all protocol, model states, and device memory events

- Ability to optionally skip initializations or dynamically change configuration parameters

- Extensive functional coverage in SystemVerilog

- Integrated with the DFI LPDDR6 solution for IP level verification

- Plug-and-play connectivity to system performance analyzer for subsystem or SoC performance verification

- Support testbench language interfaces for SystemVerilog, UVM, OVM, and SystemC

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about LPDDR IP core

LPDDR flash: A memory optimized for automotive systems

A New Generation of LPDDR

SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

On-Device AI Semiconductors & High-speed Interconnects in the Physical AI era

LPDDR6 vs. LPDDR5 and LPDDR5X: What’s the Difference?

Frequently asked questions about LPDDR IP

What is Simulation VIP for LPDDR6?

Simulation VIP for LPDDR6 is a LPDDR IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this LPDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LPDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.