Simulation VIP for I2C

The Cadence I2C VIP provides support for the I2C protocol specification.

Overview

The Cadence I2C VIP provides support for the I2C protocol specification. It provides a mature, highly capable compliance verification solution that supports simulation, protocol checking, coverage collection and analysis, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. I2C VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL). Serial, 8-bit oriented, bidirectional data transfers can be made at up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in Fast-mode, up to 1 Mbit/s in Fast-mode Plus (Fm+), or up to 3.4 Mbit/s in High-speed mode. The Ultra Fast-mode is a uni-directional mode with data transfers of up to 5 Mbit/s. The VIP meets requirements of both higher bus speeds and lower supply voltages. The VIP facilitates development of true multi-master environments with large numbers of peripherals.

Supported specification: I2C Protocol Specifications v1.0, v2.0, v2.1, v3.0, and v5.0.

Key features

- Multiple Agents

- Multi-controllers and any number of targets

- Arbitration

- Controller arbitration is supported

- Clock Stretching

- Stretching of the SCL clock

- 7-bit/10-bit Addressing

- Configurable option to use for slave addressing

- General Call

- Optional command support, configurable for each slave

- Start Byte

- Sending of optional start byte in transactions is available

- Speed Modes

- All speed modes are supported: Standard, Fast, Fast Plus, High Speed, and Ultra Fast

- Glitch Handling

- Supports optional glitch handling

- Slave Response Control

- Implements user control of slave response fields such as data, slave busy, slave sending NACK, etc.

- Software Reset

- Optional software reset command is supported

- Device ID

- Optional command Device ID is supported

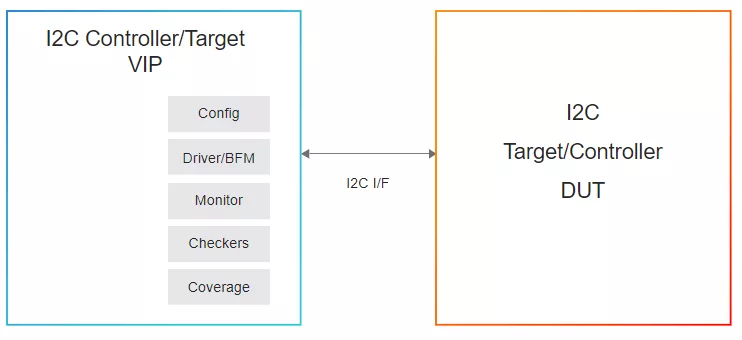

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is Simulation VIP for I2C?

Simulation VIP for I2C is a I2C / I3C IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.