Overview

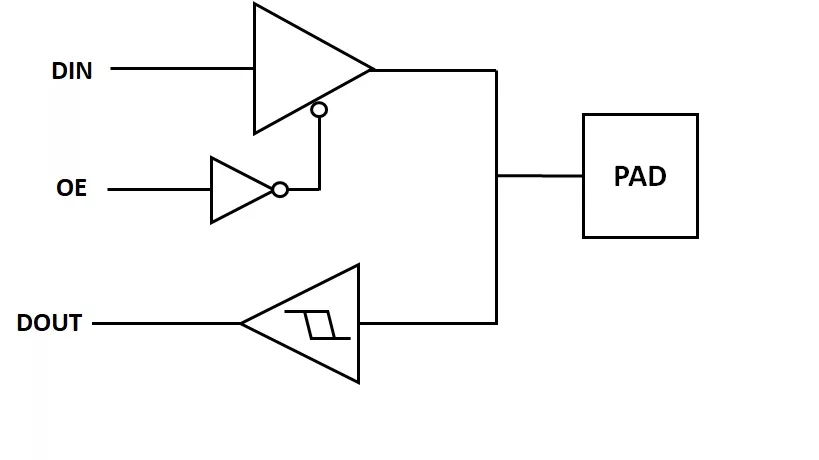

Certus is pleased to offer Secure Digital compliant IOs in advanced technology nodes. Our SD IOs support DS, HS, SDR25, SDR50, DDR50 and SDR104 protocols. Certus SD solutions are able to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation. Our SD solutions include output enable, a hysteresis receiver, and full interoperability with the feature-rich Certus General-Purpose IO libraries.

Built into our IO libraries, and also offered as a separate service, is our strong ESD expertise. Certus was founded by ESD engineers and our results speak for themselves. Not only do we consistently exceed the standard ESD targets of 2KV HBM and 500V CDM, but we also provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD and Cable Discharge Events (CDE).

Certus also offers RGMII, I2C, SMBUS, DDC, LVDS, Analog/RF, HV and numerous other IO variants across most major foundries and technology nodes. We are particularly suited at providing customized options in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

Learn more about High-Speed IP core

This post provides an in-depth look at the fundamentals of high-speed interconnects, AI/HPC trends (HBM/D2D/CPO), and the three critical requirements of Physical AI: Deterministic Latency, Functional Safety (ISO 26262), and Automotive Reliability (AEC-Q100).

Innosilicon, a leading IP provider, offers a complete PCIe 5.0 solution stack that includes both PHY and controller IPs. Although both layers are crucial to achieving a fully compliant and high-performance PCIe interface, this paper deep dives into the technical challenges of PHY design, highlighting insights drawn from real-world design margins, receiver robustness, and advanced jitter analysis in the context of Gen5 systems.

LTTPR support is quickly becoming a cornerstone of next-gen DisplayPort architectures, particularly in automotive, industrial, and multi-display environments. Here's what you need to know.

Protocol standards and speeds are advancing rapidly to boost productivity and efficiency for high-performance computing (HPC), AI training, and other applications, with the arrival of PCI Express (PCIe) 7.0 being the latest example.

Maximize limited package pins with IO that can act as high-speed test ports then be reused as low-power GPIOs during field operation.

TSMC Symposium took place from April 23, 2025, at Santa Clara Convention Center, USA.