JESD204E Controller IP

Early adopter version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters The JESD204E Contro…

Overview

Early adopter version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters

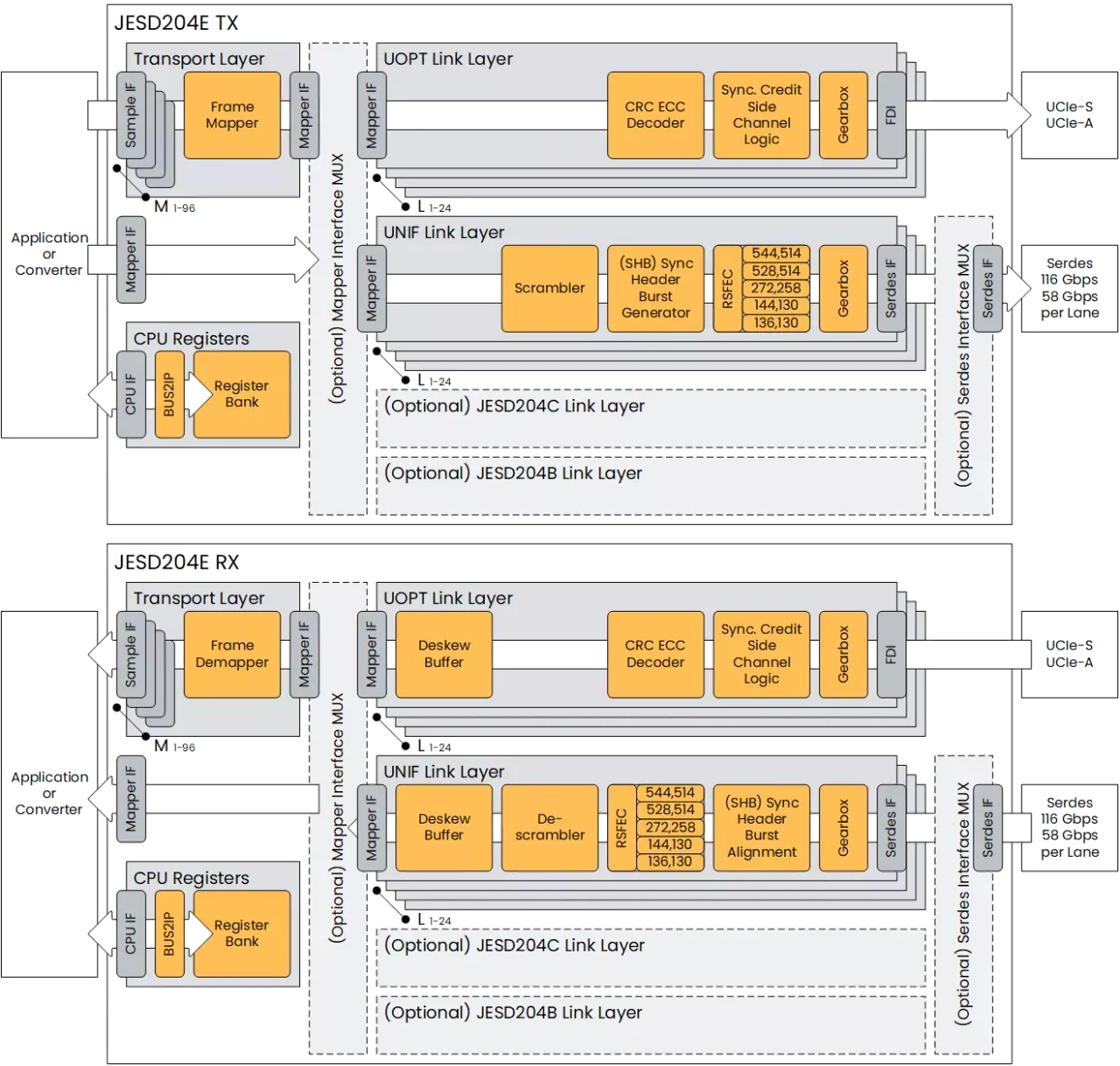

The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters. The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support. It can also include full backwards compatibility with 32.5 Gbps JESD204C.1 64b 66b link layer and 16 Gbps JESD204B 8b 10b link layer.

The IP core enables quick and reliable deployment of the transmitter (TX), the receiver (RX) link layer and comes optionally with a tightly integrated transport layer, that can dynamically be configured to handle any Multiple-Converter Device Alignment, Multiple Lanes (MCDA-ML) requirements. The IP comes with the widest parameter set available and has gone through extensive testing in a UVM regression environment.

JESD204E from Chip Interfaces is a early adopter solution with integrated transport and link layers, optional backward compatibility with JESD204B/C, and support for flexible multi-lane, multi-converter configurations. It enables high-speed connectivity to UCIe and SerDes interfaces using NRZ and PAM4, while incorporating framing, scrambling, CRC/ECC, synchronization, deskew, and centralized register control to ensure deterministic and reliable data transfer.

Key features

Delivering Performance

- UCIe Optimized Link Layer (UOPT) supports UCIe 3.0 Physical Layer with data rates up to 64Gbps for Die-to-Die based chiplet applications

- Unified Link Layer for Serdes Line rates up to 116 Gbps, with support for 1-24 lanes and 1-96 converters

- Backwards compatible with JESD204D with RS-FEC (544,514), RS-FEC (528,514), RS-FEC (272,258), RS-FEC (144,130) and RS-FEC (136,130)

Block Diagram

Benefits

Test Environment

- JESD204 IP is Tested against a VIP model in UVM regression for full functional coverage

Silicon Agnostic

- Designed in Verilog and targeting both ASICs and FPGAs

Interoperability Tested

JESD204 IP is interoperability tested with

- All leading PHY providers

- Key data converter ADC & DAC providers

PHY Integration

- PHY Integration support with additional hours or off the shelf PHY integration package for quick and efficient deployment

Active Support

All support is actively provided by engineers directly

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report , Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

What is JESD204C? A quick glance at the standard

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

Frequently asked questions about JESD204 IP cores

What is JESD204E Controller IP?

JESD204E Controller IP is a JESD204 IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.